为什么3D IC封装逐渐盛行?

随着摩尔定律面临瓶颈,3D封装技术成为集成电路发展的关键方向。

它不仅能实现电子产品的小型化,还能提升性能、降低功耗,是未来半导体行业的重要趋势。

摩尔定律遇到瓶颈

1971年,英特尔推出了全球第一款单芯片微处理器Intel 4004,从那以后,集成电路的发展一直符合摩尔定律——每颗芯片上的晶体管数量大约每18个月就翻一番。

到了1990年,为了降低发热、缩小体积、省钱,同时还要跑得更快、更省电,业界从双极晶体管转向了CMOS技术。

2000年前后,单核处理器发热太厉害了,于是多核处理器出现了。

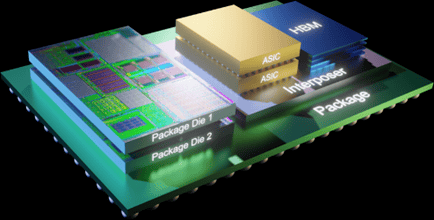

但多核处理器想要发挥性能,得有足够大的缓存和足够宽的内存带宽,这时候3D封装就派上用场了——能用相对较低的成本解决这些问题。

过去维持摩尔定律主要靠光刻技术不断缩小元件尺寸,但现在这条路越走越难、越来越烧钱。

从1970年代开始,光刻设备的价格就一路飙升,涨得比整个半导体行业的收入还快,资金压力越来越大。

3D集成技术被看作是未来降低成本的关键,它给了我们第三个维度,让芯片能继续做得更密、功能更多、性能更好,关键是成本还能降下来。

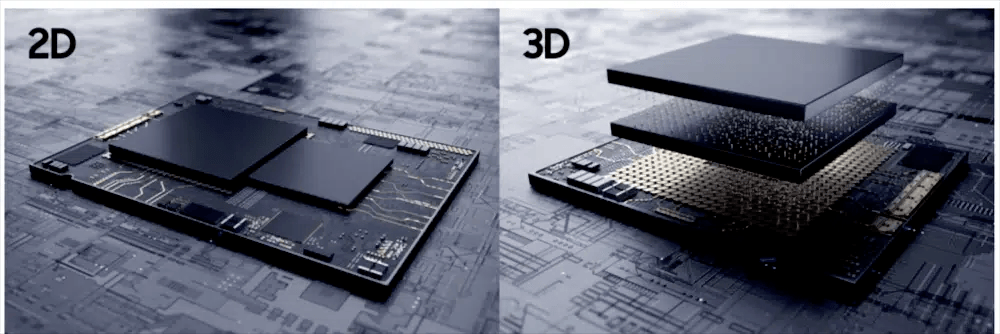

产品要做小,必须用3D封装

现在的电子产品都要求轻薄短小,这就得用3D封装。

用了3D封装的硅芯片一般只有50-100微米厚,比传统封装薄了九成。

基板厚度也就0-100微米,同样比传统的薄了九成多。

高密度互连的直径只有5-20微米,比2D封装小了九成以上。

所以改用3D封装,尺寸和重量能大幅缩减。

做小型化产品,芯片在电路板上占的地方得小。

3D封装就是把多颗芯片摞起来,这样一来,占用的面积就小多了。

性能更好,功耗更低

3D封装最大的好处是把连线距离大大缩短了。

2D封装里,典型的连线长度有4毫米;换成3D封装,只要200微米就够了。

而且3D封装的连线利用率也好得多。

在2D封装里,中间那颗芯片只能连到周围8个芯片;用3D封装叠起来后,同样的连线长度,中间的芯片能连到116个芯片。

连线短了,利用率高了,信号延迟自然就小了——要知道延迟主要就是信号在连线上跑的时间。

延迟低、总线宽,带宽自然就上去了。

设计合理的3D系统里,各种噪声——反射、串扰、同步开关、电磁干扰——都会因为连线变短而降低。

还有,寄生电容跟连线长度成正比,连线短了,寄生电容小了,功耗也就下来了。

省下的电让3D器件能跑得更快,但功耗反而更低。

总的来说,用了3D封装技术,整个系统性能都能上一个台阶。