算力达GPU千倍!北大芯片突破登Nature子刊

芯东西(公众号:aichip001)

编译 | 程茜

编辑 | Panken

芯东西10月17日消息,10月13日,北京大学AI研究院孙仲研究员团队及合作者的新研究成果,登上国际顶级学术期刊Nature子刊Nature Electronics。

该团队成功研制出基于阻变存储器的高精度、可扩展模拟矩阵计算芯片,将传统模拟计算的精度提升了五个数量级,首次将模拟计算的精度提升至24位定点精度,可与数字计算媲美。

论文提到,相关性能评估表明,该芯片在求解大规模多输入多输出(MIMO)信号检测等关键科学问题时,在相同的精度下,该模拟计算方法可以提供比最先进的GPU高1000倍的吞吐量和100倍的能效。

孙仲认为,这项进展能在未来的6G通信领域让基站实时、低能耗处理海量天线信号,提升网络容量和能效;在AI领域其有望加速大模型训练中计算密集的二阶优化算法从而提升训练效率,此外其低功耗特性也可支持复杂信号处理和AI训推一体在终端设备上的直接运行,推动边缘计算发展。

这一成果标志着我国突破模拟计算世纪难题,在后摩尔时代计算范式变革中取得重大突破,为应对AI与6G通信等领域的算力挑战开辟了全新路径。

论文的题目为《基于阻变存储器芯片的高精度、可扩展模拟矩阵方程求解技术(Precise and scalable analogue matrix equation solving using resistive random-access memory chips)。该研究由北京大学AI研究院通用AI芯片研究中心主导,并联合集成电路学院研究团队完成,孙仲课题组在项目攻关中发挥了核心作用,是此项成果的主要贡献者。

▲Nature Electronics论文发布主页

论文地址:https://www.nature.com/articles/s41928-025-01477-0

一、让模拟计算兼顾高精度、可扩展性是世纪难题

在传统器件尺寸缩放逼近物理极限、传统冯·诺依曼架构面临“内存墙”瓶颈的双重背景下,高复杂度计算给传统数字计算机带来了严峻挑战。

模拟计算具备通过物理定律直接实现高并行、低延时、低功耗的先天优势,但此前传统模拟计算因受限于低精度、难扩展等缺点使其逐渐被数字计算所取代。

当下,孙仲认为:“如何让模拟计算兼具高精度与可扩展性,从而在现代计算任务中发挥其先天优势,一直是困扰全球科学界的‘世纪难题’。”

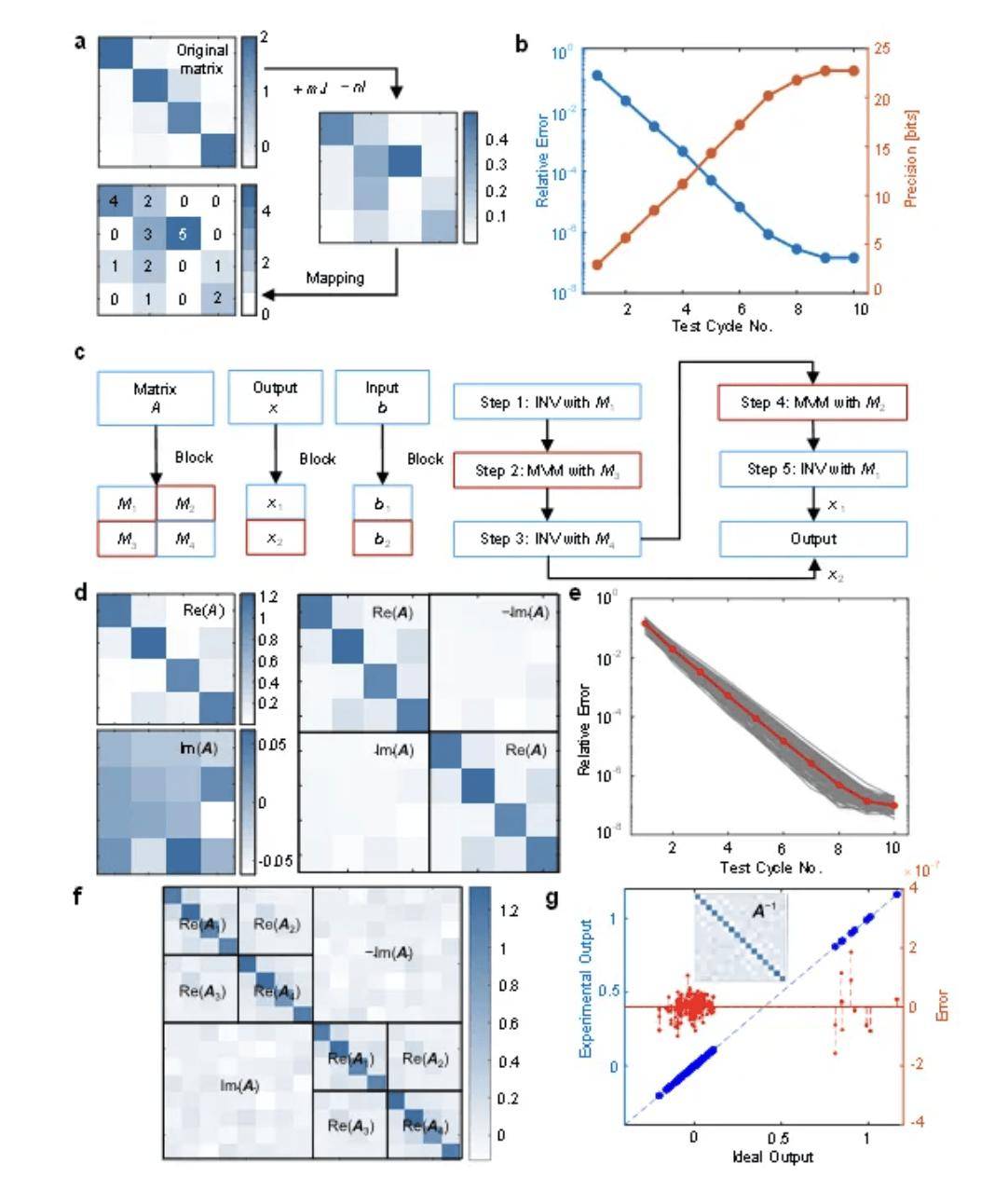

解决这一难题的可行路径是基于阻变存储器阵列的模拟矩阵计算技术(AMC),基于“阵列-运算放大器”闭环反馈原理设计的矩阵求逆电路,能够实现矩阵求逆的一步式求解。其可以通过在阻变存储器阵列和运算放大器(OPA)等传统模拟元件之间建立闭环反馈,所得电路可以一步解决矩阵反转(INV)。

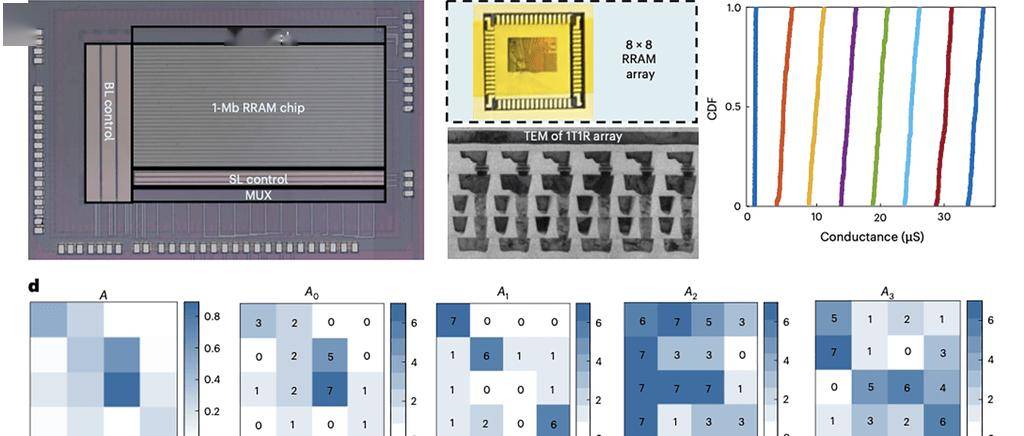

▲模拟矩阵计算电路求解矩阵方程

但这类电路的低精度特性、电路的硬连接结构仍是挑战。

此外,在模拟矩阵乘法计算中,比特切片、模拟补偿可用于精确执行矩阵向量乘法,但使用此类技术求解矩阵方程具有挑战性,矩阵方程求解过程缺乏有效的分配律与分块矩阵方法支撑,这使得使得解决模拟INV的精度和可扩展性问题具有挑战性。

论文提到,其中一种解决方案是采用模拟-数字混合设计。以前的方法将基于MVM的低精度迭代模拟求解器结合在迭代细化算法中,浮点数字计算机用于执行高精度MVM(HP-MVM)运算,收敛到准确的结果。

但这种方案会削弱模拟计算在降低复杂性方面的优势,并且需模拟-数字转换,导致矩阵方程求解性能只能逐步提高。模拟INV仅限于具有无源电阻随机存取存储器(RRAM)阵列的小规模电路,这不利于晶圆代工制造,并且缺乏可靠的多级存储器特性。

二、提出高精度、可拓展全模拟矩阵方程求解器,首次将模拟计算精度提升至24位定点精度

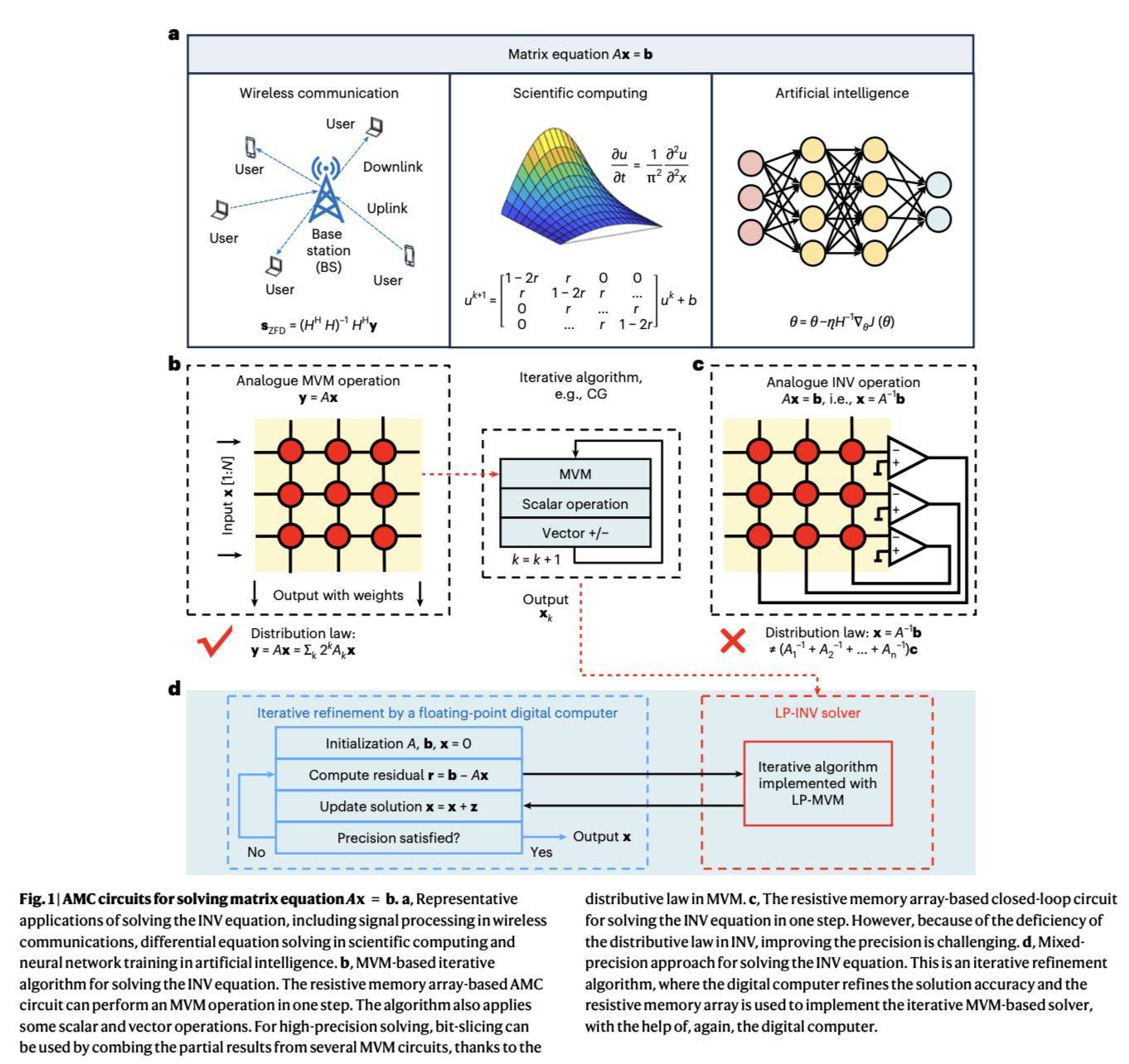

在此基础上,北京大学AI研究院孙仲研究员团队提出了一种基于阻变存储器阵列的高精度、可拓展的全模拟矩阵方程求解器。

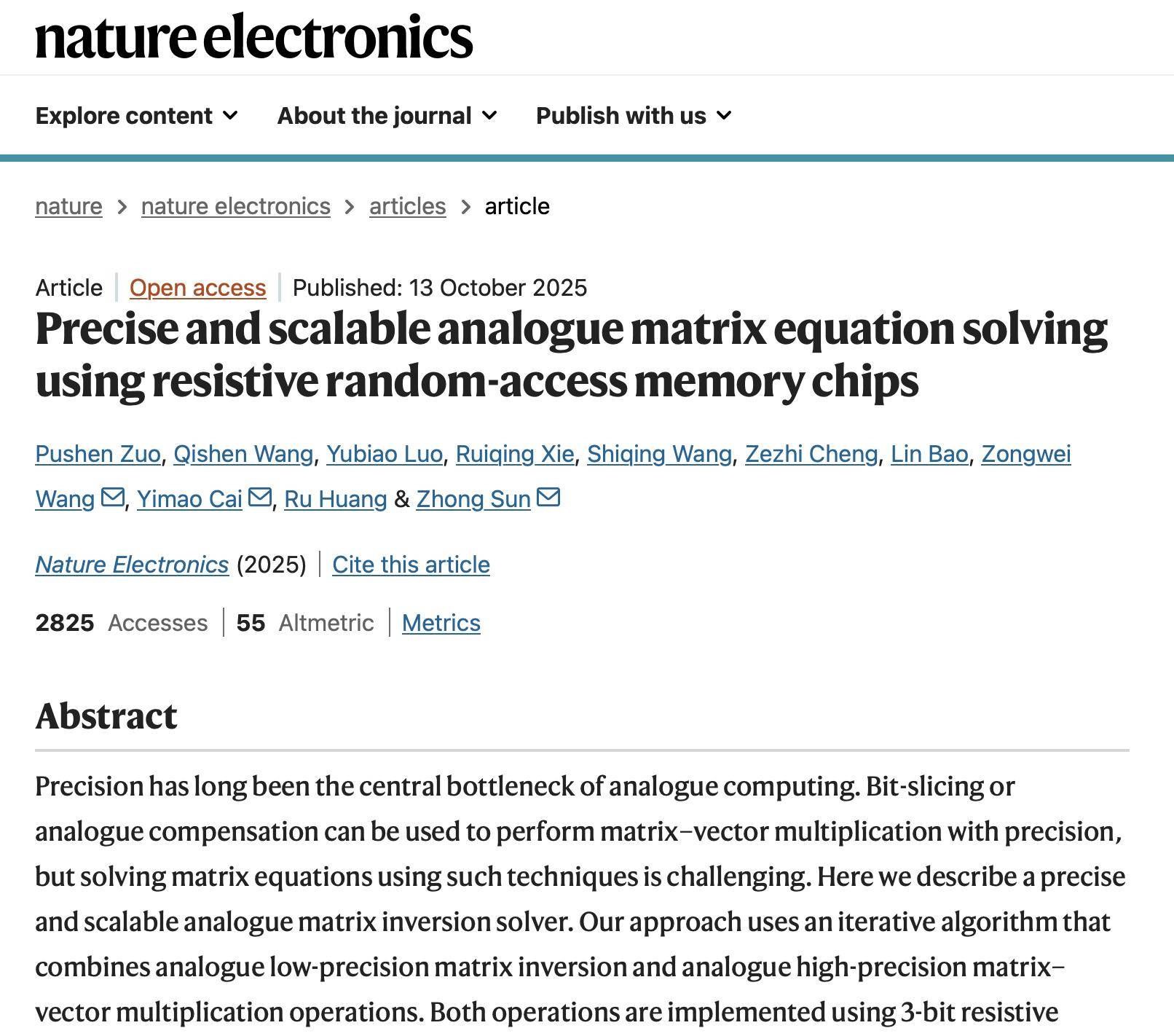

该方案使用一种迭代算法,结合了模拟低精度矩阵求逆(LP-INV)和模拟高精度矩阵向量乘法(HP-MVM)运算,通过将这些芯片与分块矩阵算法相结合,首次将模拟计算的精度提升至24位定点精度。模拟INV通过在每次迭代中提供近似正确的结果来减少迭代次数,高精度模拟MVM则通过比特切片实现。

此外,模拟低精度矩阵求逆和模拟高精度矩阵-向量乘法运算两个电路的阻变存储器阵列在40nm CMOS工艺平台制造,可实现3比特电导态编程。

▲高精度全模拟矩阵计算求解矩阵方程

研究团队还在硬件中验证了BlockAMC方法,该方法使用块矩阵求解大规模矩阵方程,并使用它来求解中等规模16×16矩阵方程。

具有模拟矩阵运算的HP-INV方案,由LP-INV和HP-MVM作的迭代组成,两者均由AMC电路实现。HP-INV方法可以扩展到求解实值和复值矩阵方程,这些矩阵方程经常出现在科学计算中的微分方程和无线通信中的信号处理等应用中。

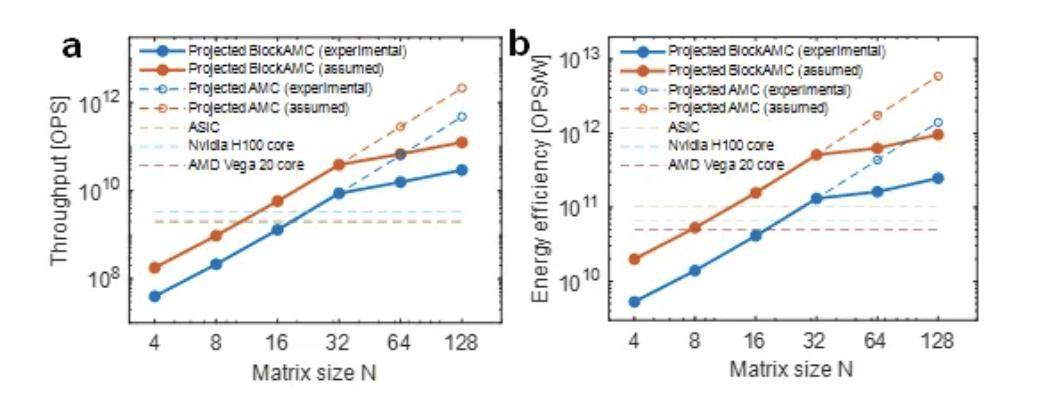

研究人员评估了导线电阻对HP-INV收敛率的潜在影响,与基于RRAM的MVM应用相比,在片上构建大规模INV电路更具挑战。尽管如此,32×32至64×64的阵列已经可以在吞吐量和能效方面提供显著增益,尽管它比典型的基于RRAM的MVM电路小得多。

目前其对于LP-INV的演示仍然仅限于8×8个阵列,扩展到更大的32×32实现将需要专用的芯片设计和流片验证。

研究团队认为,对于此类设计,将中等规模的LP-INV与HP-MVM集成在单个芯片上将特别有价值,并且应该成为未来研究的主要焦点。

三、计算吞吐量、能效是GPU的千倍、百倍,可应用于大规模输入输出

该方案实现了计算精度提升,通过与块矩阵算法相结合,研究团队在实验上成功实现了16×16矩阵的24比特定点数精度求逆,也就是矩阵方程求解经过10次迭代后,相对误差可低至10⁻⁷量级。

▲基于块矩阵方法求解高精度、可拓展矩阵方程的实验结果

在计算性能方面,北京大学AI研究院公众号提到,其测试结果表明,在求解32×32矩阵求逆问题时,其算力已超越高端GPU的单核性能;当问题规模扩大至128×128时,计算吞吐量更达到顶级数字处理器的1000倍以上。

能效比方面,其在相同精度下能效比传统数字处理器提升超100倍。

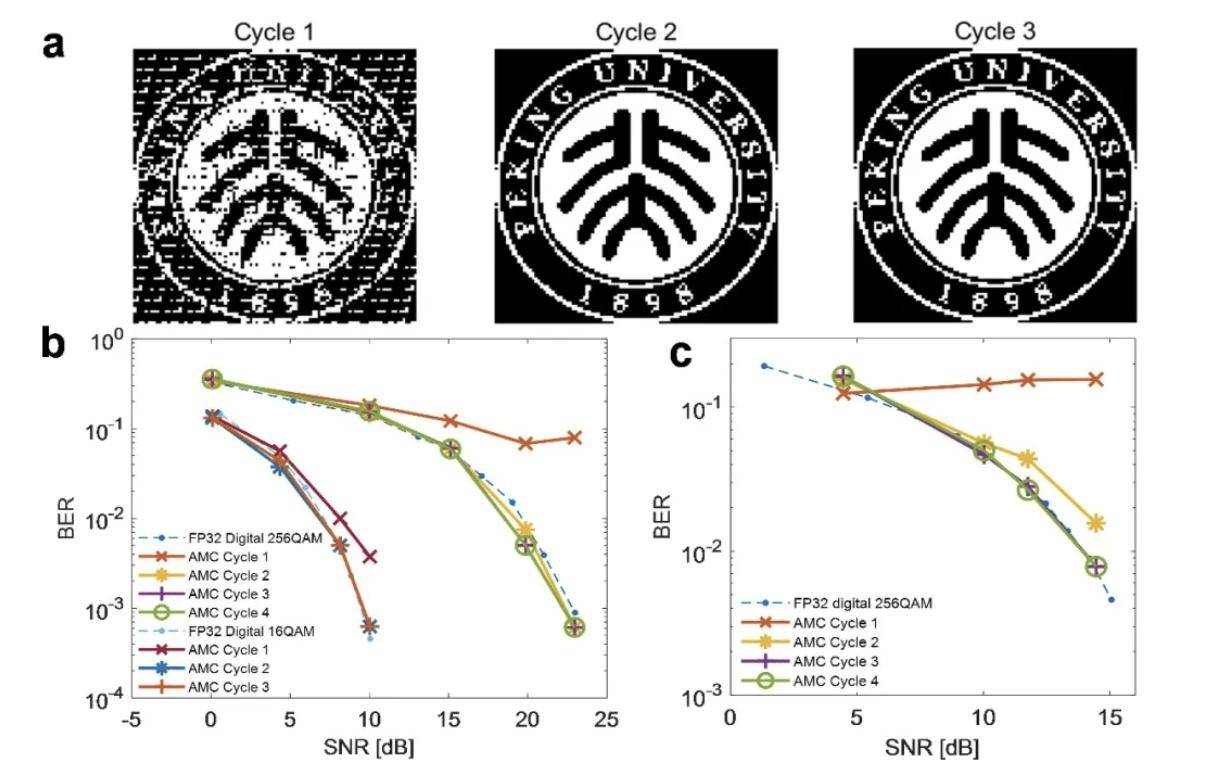

在应用验证层面,大规模多输入多输出(MIMO)技术有望在5G-A和6G时代大幅提高无线通信系统的服务质量,但在大规模MIMO中,基站(BS)的天线数量远大于用户设备的天线数量。

模拟求解器可应用于大规模MIMO系统的检测过程,与采用256-QAM调制的128×8系统的数字求解器相比,仅在三个迭代周期内就显示出相同的误码率性能。

▲高精度矩阵方程求解在大规模多输入多输出(MIMO)迫零检测信号处理过程中的应用

综合基准测试结果证实,在保持相当计算精度的前提下,该模拟计算方法可实现领先的处理速度和能效。

结语:为算力提升探索出一条极具潜力的路径

这篇论文提出的基于阻变存储器阵列的高精度、可拓展的全模拟矩阵方程求解器,为应对AI与6G通信等领域的算力挑战开辟了全新路径。

孙仲认为,这项突破的意义远不止于一篇顶刊论文,它的应用前景广阔,可赋能多元计算场景,有望重塑算力格局,“这项工作的最大价值在于,它用事实证明,模拟计算能以极高效率和精度解决现代科学和工程中的核心计算问题。可以说,我们为算力提升探索出一条极具潜力的路径,有望打破数字计算的长期垄断,开启一个算力无处不在且绿色高效的新时代。”