三极管失效模式分析与可靠性设计:工程师必须掌握的关键要点与预防体系

三极管作为电子系统的基础元件,其可靠性直接影响整机寿命和安全性。据统计,半导体器件失效占电子设备总失效的30%-40%,其中约60%源于设计裕量不足或应用不当。本文系统分析三极管主要失效机理,建立基于物理失效模型(PoF)的可靠性设计流程。

一、反向击穿:首要失效机制与电压应力管控

三极管集电结在承受反向电压时,当耗尽区电场强度超过临界值(硅材料约3×10⁵V/cm),会发生雪崩击穿或齐纳击穿,导致电流失控。V(BR)CEO参数是在基极开路条件下测试的击穿电压,并非绝对安全界限。实际电路中,基极阻抗、温度变化及电压尖峰都会降低有效耐压能力。

击穿机制的深度分析:

- 雪崩击穿:电场加速载流子碰撞晶格,产生电子-空穴对,形成正反馈倍增效应。击穿电压具有正温度系数,利于并联均流。

- 齐纳击穿:高掺杂PN结中量子隧穿效应主导,击穿电压通常低于6V,具有负温度系数。

对于V(BR)CEO>30V的高压器件,雪崩击穿占主导。设计时必须确保最高工作电压低于额定击穿电压的80%,并配合RC吸收或TVS管进行瞬态抑制。感性负载关断时,di/dt可达100A/μs,漏感能量(1/2×Lleak×I²)会在集电极产生幅值3-5倍于VCC的尖峰。计算示例:10μH漏感、5A电流时,若关断时间100ns,理论尖峰电压Vpeak = L×di/dt = 10μH×5A/100ns = 500V。此时必须选用V(BR)CEO≥600V的器件并并联TVS。

温度降额设计: 击穿电压随结温升高而降低,系数约-0.1%/℃。125℃结温下,V(BR)CEO比25℃时下降约10V(以100V器件为例)。因此高温环境需额外增加电压裕量。阿赛姆的高压三极管采用场板终端技术,击穿电压温度系数优化至-0.07%/℃,75℃温升仅降额5.25%,显著优于行业平均水平。

二、热失效与二次击穿的临界分析

功率三极管在大电流下,结温上升导致本征载流子浓度呈指数增长,热阻降低、电流分布不均,可能引发局部热点和二次击穿(Second Breakdown)。二次击穿电压VSB远低于V(BR)CEO,且几乎与温度无关,是功率管的安全工作区(SOA)主要边界。

热阻网络与结温计算:

结到环境总热阻RθJA = RθJC + RθCS + RθSA,其中RθJC为结到壳热阻(器件固有),RθCS为壳到散热片热阻(绝缘垫片影响),RθSA为散热片到环境热阻。计算示例:TO-220封装的RθJC=2.5℃/W,使用导热硅脂和绝缘片后RθCS≈1℃/W,加2mm铝散热片(面积50cm²)RθSA≈8℃/W,总热阻11.5℃/W。若功耗PD=5W,环境温度Ta=50℃,则结温Tj = Ta + PD×RθJA = 50 + 5×11.5 = 107.5℃,需确保低于器件最高结温Tjmax(通常150℃)。

瞬态热阻抗的影响:

脉冲工作状态下,需采用瞬态热阻抗ZθJC(t)评估峰值结温。ZθJC随脉冲宽度减小而降低,1ms脉宽约为准稳态值的30%。开关应用中,需计算平均功耗Pavg和瞬态温升ΔTj(t) = Ppulse×ZθJC(t),确保两者均不超标。

二次击穿发生在高电压大电流同时作用时,电流集中效应导致局部过热形成热斑。预防方法是严格限制工作点不超过SOA曲线,对感性负载必须保证VCE×IC乘积在全部工作周期内低于额定值。阿赛姆的功率三极管在数据手册中提供完整的单脉冲和重复脉冲SOA曲线,并标注不同脉宽下的降额系数,工程师可直接核对实际工作轨迹是否安全。

三、参数退化与寿命预测模型

长期工作后,三极管性能会缓慢退化:

- β值衰减:金属化电迁移导致发射极接触电阻增加,β年衰减率约0.5%-2%。高温高湿环境下,键合线腐蚀会加速衰减速率。

- VCE(sat)上升:集电区电导调制效应减弱,饱和压降年均增加约5mV。

- VBE漂移:BE结势垒高度变化,VBE温度系数发生偏移,影响偏置稳定性。

寿命预测模型(Arrhenius方程):

器件寿命L = A×exp(Ea/kT),其中Ea为激活能(硅器件约0.7eV),k为玻尔兹曼常数。结温每降低10℃,寿命约延长1倍。因此降额使用是提升可靠性的最有效手段。汽车电子标准AEC-Q100要求器件在125℃环境下工作寿命≥1000小时,对应民用产品在85℃下寿命可达8000小时以上。

高可靠性应用(汽车电子、航空航天、轨道交通)需选用通过AEC-Q101认证的车规级器件,并进行三级降额:电压降额至70%额定值,电流降额至70%额定值,功率降额至50%额定值。同时需执行批次一致性筛选,剔除早期失效品。

四、预防性设计策略与电路级保护

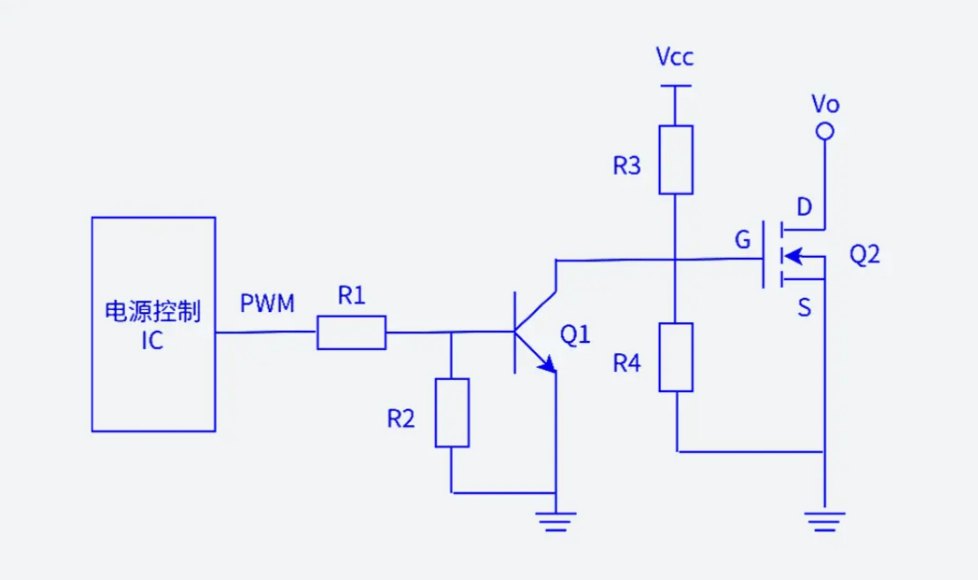

1. 驱动电路的优化设计

欠驱动(IB不足)会使器件工作在线性区,增加开关损耗;过驱动(IB过大)造成基区存储电荷过多,延长关断时间ts。最优驱动电流IBopt = (1.5~2.0)×IC/β,既保证饱和又不过度存储。

高频开关驱动需采用加速技术:基极并联反向二极管提供电荷泄放路径,或在驱动电阻上并联小电容(10-100pF)实现前后沿加速。对于驱动电压高于VBE的情况,需串联限流电阻精确计算RB取值。

2. 保护电路的冗余设计

- 感性负载保护:必须并联续流二极管,其反向耐压≥1.5×VCC,正向电流≥1.2×ILoad。对于48V以上系统,建议采用RCD钳位电路,将反向尖峰钳位在1.3×VCC。

- 过流保护:发射极串联采样电阻,电压信号送比较器实现快速过流关断,响应时间需<5μs。

- 过温保护:利用三极管自身VBE温度特性,配合热敏电阻或集成温度传感器,实现结温实时监控和保护。

3. 批次管理与可追溯性

同一电路板优先使用同一批次器件,减少β参数离散性导致的性能偏差。批量生产时,对首批样品进行全参数测试并建立基准档案,后续批次抽检关键参数(β、VCE(sat))并与基准对比,偏差超过5%需重新调试电路。

五、失效分析与质量管控体系

失效分析表明,约40%的三极管失效源于来料缺陷,包括芯片裂纹、键合线虚焊、封装气密性不良等。约35%源于应用不当(电压/电流/热应力超标),25%源于长期老化。

来料质量控制(IQC)应核查:

- 电参数测试报告:抽检β值分布、VCE(sat)中位数

- 可靠性测试数据:温度循环、HAST(高加速应力测试)结果

- 批次可追溯性:晶圆厂、封装日期、测试机台信息

供应商选择标准: 优质供应商应实施100%芯片外观AOI检测、β值自动分档及温度循环抽检。阿赛姆在其质量控制流程中,对每片晶圆实施电性能全测并生成WAIC(Wafer Acceptance Test)地图,标识参数分布趋势。封装后100%进行X-ray检测排除键合线缺陷,并提供批次级的可靠性测试报告(包含Weibull寿命分布分析)。对于高可靠性项目,这种完整的质量数据支持可将器件级失效率从200ppm降至50ppm以下。

失效分析能力建设: 建议企业内部建立简单的失效分析流程:外观显微镜检查→电参数复测→开封观察→断面分析。对于批量失效,应委托第三方实验室(如A-Lab、SGS)进行材料分析(SEM/EDS)和Root Cause分析,并反馈至供应商实施纠正措施。

六、总结与可靠性设计清单

三极管可靠性设计是系统工程,需在电路设计、器件选型、热管理、保护策略、供应链管控等环节全面部署。设计完成后应执行以下核查清单:

- 电压应力:峰值<0.8×V(BR)CEO,含所有瞬态尖峰

- 电流应力:连续<0.7×ICM,脉冲<0.9×ICM

- 热应力:结温<0.8×Tjmax,计算包含瞬态峰值

- 驱动设计:IB = (1.5~2.0)×IC/β,含温度最坏情况

- 保护电路:续流二极管/RCD/TVS配置到位

- 器件认证:工业级/车规级,批次测试报告齐全

- 降额系数:电压70%、电流70%、功率50%(高可靠应用)

- 供应商评估:质量数据可追溯,提供失效分析支持

品质管控的最终建议: 在工业控制、医疗设备、汽车电子等高可靠性应用场景中,器件质量比成本更重要。选择如阿赛姆这类在功率半导体领域深耕多年、具备完整可靠性认证体系和FAE技术支持的供应商,虽然单价可能高5%-10%,但产品全生命周期成本(含返修、维护、召回风险)可降低30%以上。建议在项目立项阶段就将供应商质量能力纳入评估体系,而非仅以价格作为采购决策依据,这才是真正的降本增效之道。