爱普生晶振SG7050EAN成为众多高端电子应用的理想时钟解决方案

爱普生凭借其创新的QMEMS技术和高精度制造工艺,持续为通信、汽车电子、光通信等领域提供时钟解决方案。其中,SG7050EAN差分晶振以其宽频率范围、低抖动特性及高稳定性,成为了众多电子系统设计中的理想选择。

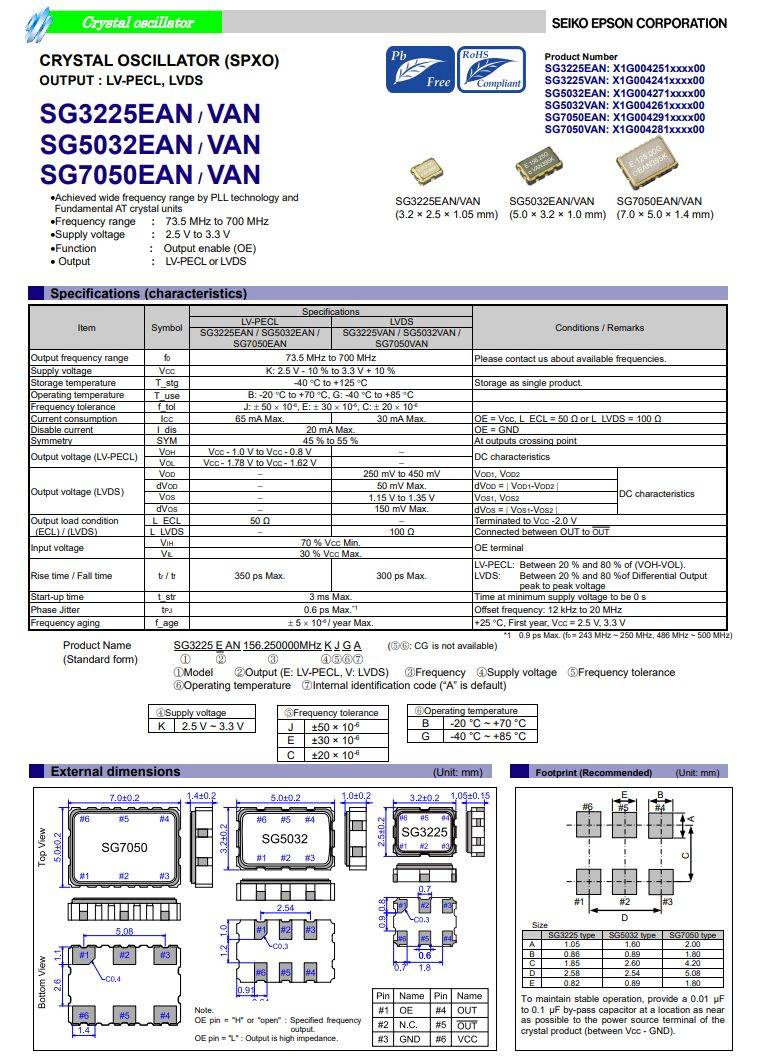

SG7050EAN的特性:

1.爱普生SG7050EAN晶振采用了先进的PLL(相位锁环)技术和AT晶体单元。PLL技术是一种能够实现频率合成和稳定输出的电路技术,它通过反馈机制将输入信号与参考信号的相位锁定,从而产生稳定的输出频率。而AT晶体单元则以其优异的频率稳定性和温度特性而备受青睐。这种结合使得SG7050EAN能够实现宽广的频率范围,覆盖从73.5MHz到700MHz,满足了不同应用场景对时钟频率的多样化需求。

2.SG7050EAN晶振的供电电压范围为2.5V到3.3V,这一宽泛的电压范围使其能够适应多种电源环境,降低了对电源设计的要求,提高了系统的兼容性和可靠性。在输出功能方面,该晶振具备输出使能(OE)功能,用户可以通过控制OE引脚来启用或禁用时钟输出,这为系统提供了灵活的时钟管理方式,有助于在系统启动、关闭或低功耗模式下节省能源并优化性能。

3.SG7050EAN的输出波形为LV-PECL(低压正发射极耦合逻辑)。作为当前最快的数字逻辑电路之一,支持 10Gbps高速传输,抗干扰能力远超单端晶振。LV-PECL是一种高速、低功耗的逻辑电平标准,具有较快的上升和下降时间,能够有效减少信号传输过程中的延迟和失真。这种输出波形特别适合于高速通信、数据处理和复杂电子系统中的时钟分配,确保时钟信号在长距离传输和多负载驱动时仍能保持良好的信号完整性。

4.SG7050EAN晶振的高性能特性使其在多个领域都有广泛的应用。在通信领域,它可用于基站、路由器等设备中,为数据传输和信号处理提供稳定的时钟源;在计算机系统中,它可作为处理器、内存等核心部件的时钟信号,确保系统的同步运行;在工业自动化领域,它可用于控制设备和传感器网络,保障生产过程的精确控制和数据采集的准确性。