驱动IC两级关断(2LTO)确立为碳化硅MOSFET短路保护最佳配置的机理解析

驱动IC两级关断(2LTO)确立为碳化硅MOSFET短路保护最佳配置的物理机制与工程原理深度研究报告

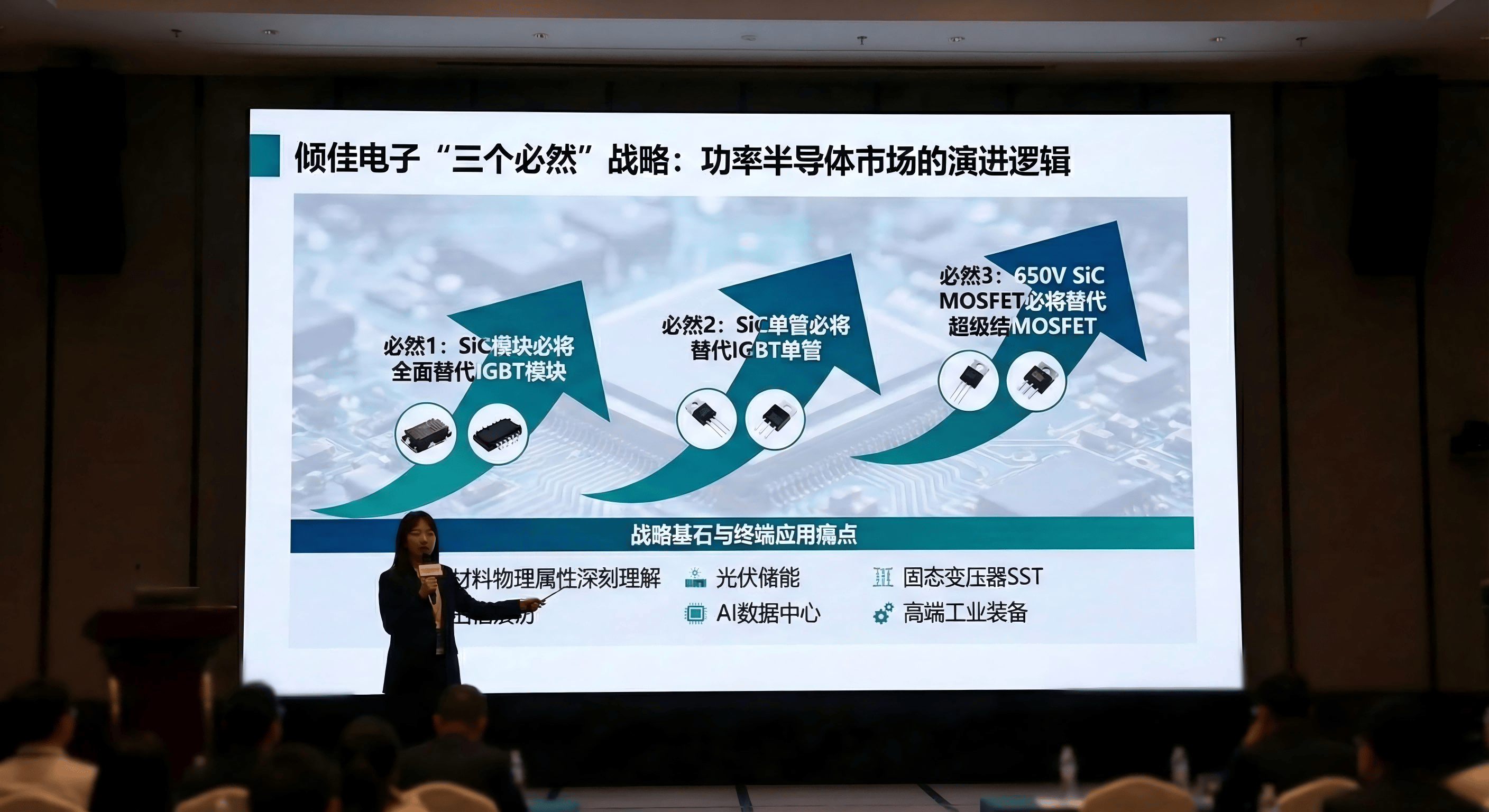

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 绪论:宽禁带半导体时代的保护悖论

碳化硅(Silicon Carbide, SiC)金属氧化物半导体场效应晶体管(MOSFET)的商业化普及,标志着电力电子技术进入了一个以高频、高压、高功率密度为特征的新纪元。得益于碳化硅材料宽禁带(3.26 eV)、高临界击穿电场(约为硅的10倍)以及高热导率的物理特性,SiC MOSFET在高压电源转换系统、固态变压器SST、储能变流器PCS、Hybrid inverter混合逆变器、户储、工商业储能PCS、构网型储能PCS及可再生能源并网设备中展现了无可比拟的性能优势 。

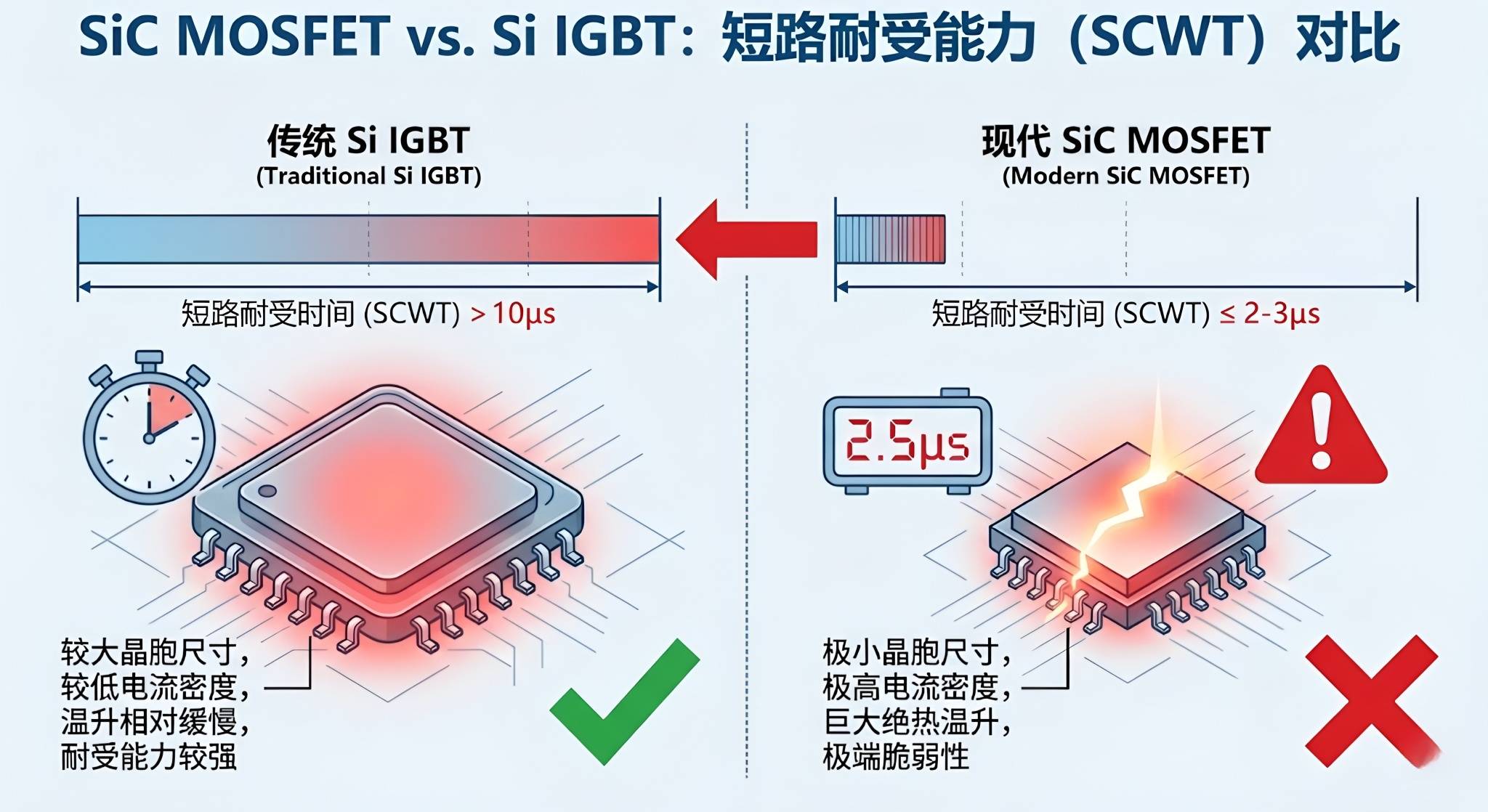

然而,这种性能的跃升并非没有代价。SiC MOSFET在极大地降低开关损耗和导通电阻的同时,显著牺牲了短路耐受能力(Short Circuit Withstand Time, SCWT)。相比于传统的硅基绝缘栅双极型晶体管(Si IGBT)通常具备10微秒以上的短路耐受时间,现代SiC MOSFET的SCWT往往被压缩至2至3微秒甚至更短 。这种极端的脆弱性源于SiC芯片极小的晶胞尺寸和极高的电流密度,导致在短路发生时,器件内部即刻产生巨大的绝热温升。

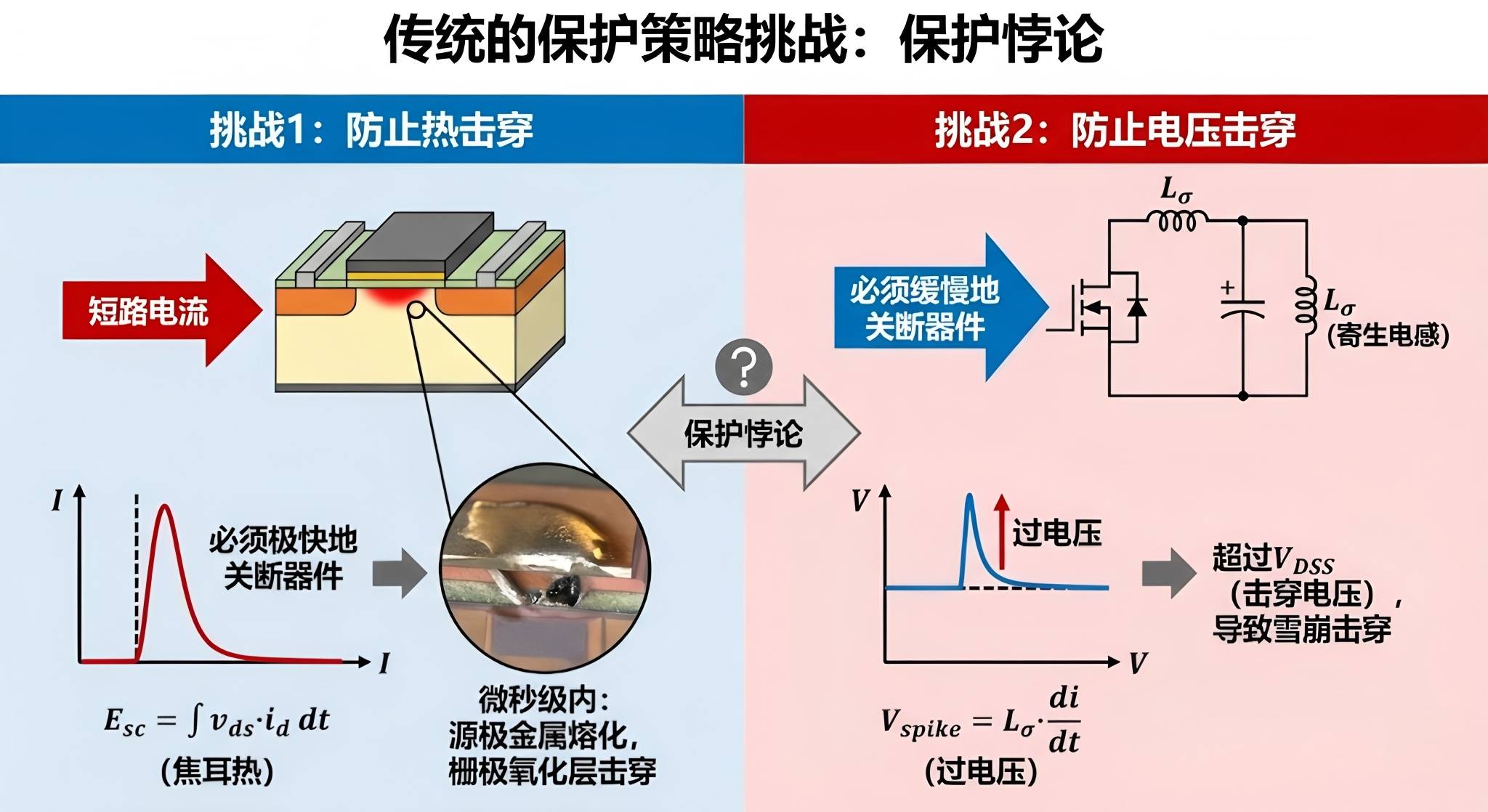

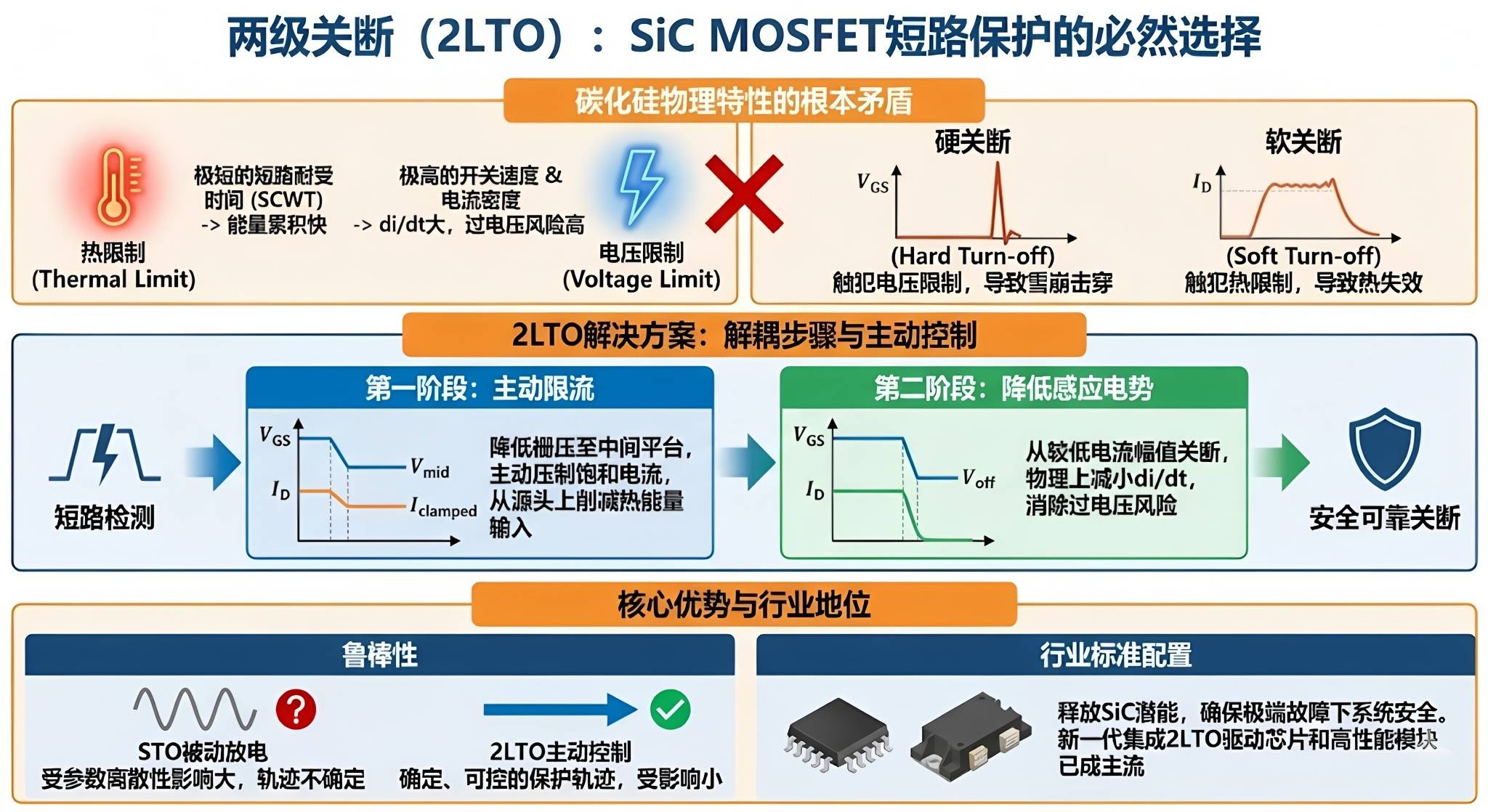

在这一背景下,传统的保护策略遭遇了严峻的挑战,即所谓的“保护悖论”:

- 为了防止热击穿,必须极快地关断器件: 短路电流产生的焦耳热(Esc=∫vds⋅iddt)在微秒级时间内即可熔化源极金属或击穿栅极氧化层。

- 为了防止电压击穿,必须缓慢地关断器件: 极快的电流变化率(di/dt)在回路寄生电感(Lσ)上感应出巨大的过电压(Vspike=Lσ⋅di/dt),叠加在直流母线电压上极易超过器件的漏源击穿电压(VDSS),导致雪崩击穿。

如何在“热毁灭”与“电压毁灭”的夹缝中寻求生存,成为了SiC栅极驱动设计的核心难题。本报告将深入剖析为何**两级关断(Two-Level Turn-Off, 2LTO)**技术——一种通过在关断过程中引入中间电压平台的策略——成为了解决这一悖论的根本性物理方案。我们将结合半导体物理特性、电路暂态分析以及来自基本半导体(BASiC Semiconductor)、德州仪器(TI)、英飞凌(Infineon)等厂商的实测数据,全面论证2LTO作为SiC MOSFET短路保护最佳配置的必然性。

2. 碳化硅MOSFET短路失效的物理机制

要理解保护配置的根本原因,首先必须从微观物理层面解构SiC MOSFET在短路工况下的行为特征。与Si IGBT不同,SiC MOSFET的失效机制主要由其独特的转移特性和热容特性决定。

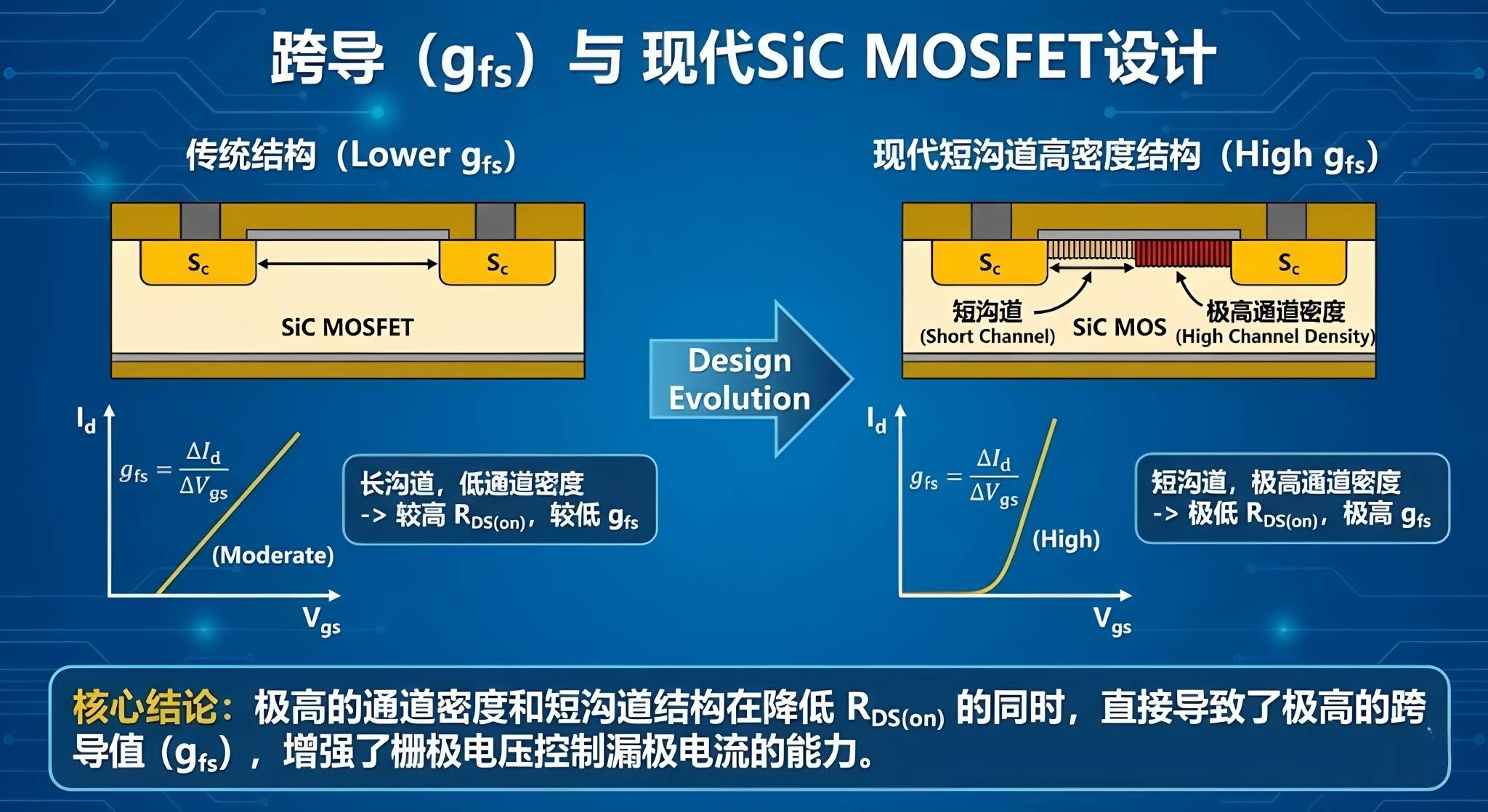

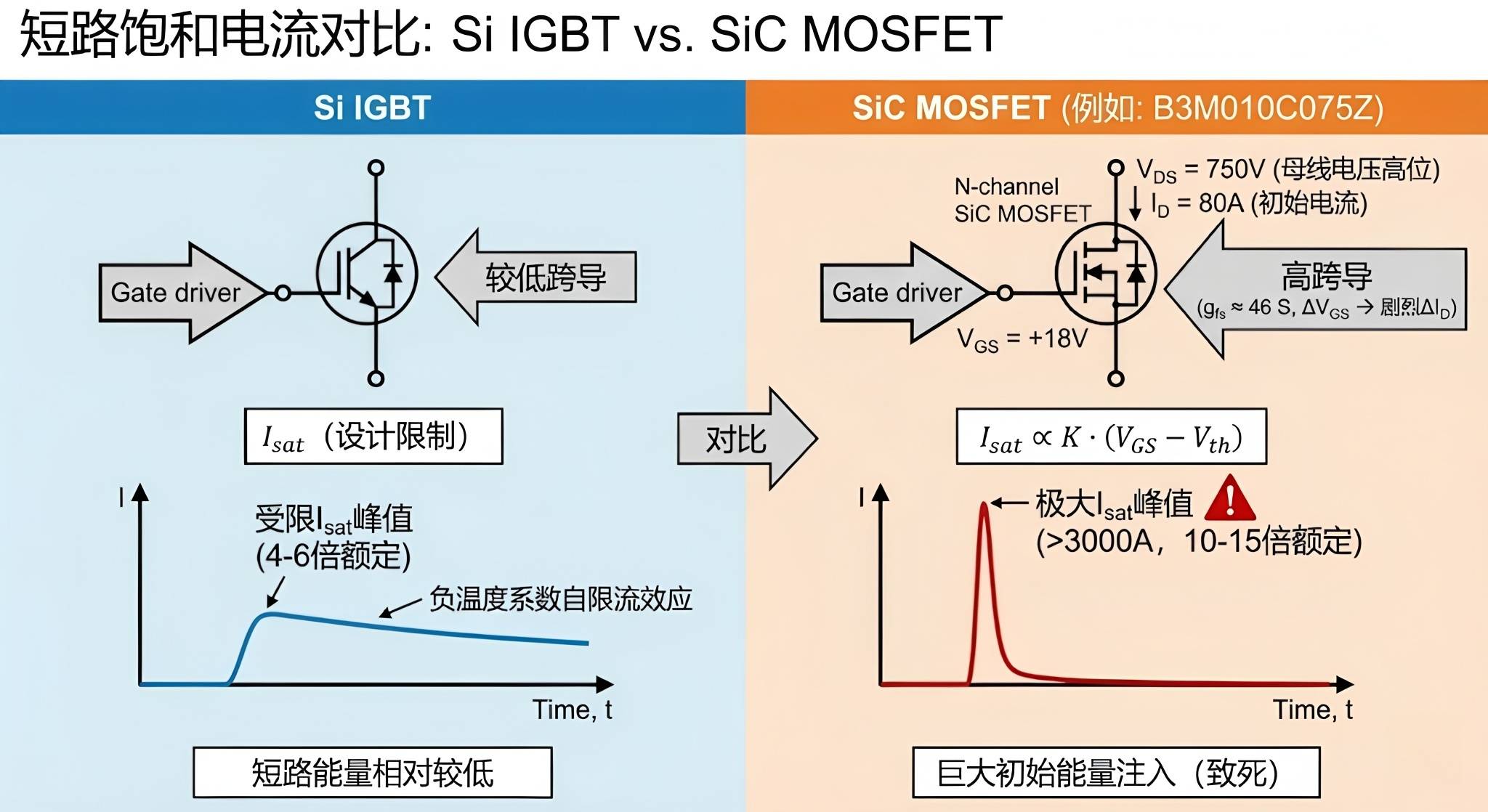

2.1 高跨导与饱和电流的无节制

跨导(Transconductance, gfs)是衡量MOSFET栅极电压控制漏极电流能力的关键参数。为了降低导通电阻(RDS(on)),现代SiC MOSFET设计采用了极高的通道密度和短沟道结构,这直接导致了极高的跨导值。

根据基本半导体B3M010C075Z(750V/240A)的数据手册,其在VDS=10V,ID=80A时的典型跨导高达46 S 。这意味着栅极电压的微小变化都会引起漏极电流的剧烈波动。在短路发生时,漏极电压VDS维持在母线电压高位,器件运行在饱和区。此时的饱和电流(Isat)主要由栅源电压(VGS)决定:

Isat∝K⋅(VGS−Vth)

由于SiC MOSFET通常推荐使用+18V的高栅极驱动电压以降低通态损耗,结合其高跨导特性,导致其短路饱和电流可以达到额定电流的10倍甚至15倍 。

对比分析:

- Si IGBT: 饱和电流通常被设计限制在额定电流的4-6倍,且具有负温度系数的自限流效应(在短路期间电流会略微下降)。

- SiC MOSFET: 饱和电流极大(例如,额定360A的BMF360R12KA3模块,其短路电流峰值可能瞬间突破3000A),且随着沟道温度升高,虽然迁移率下降会略微降低电流,但巨大的初始电流密度已经注入了致死能量。

这种巨大的饱和电流意味着在短路发生的最初几微秒内,器件内部的功率密度达到了兆瓦(MW)级别,远超器件的承受范围。

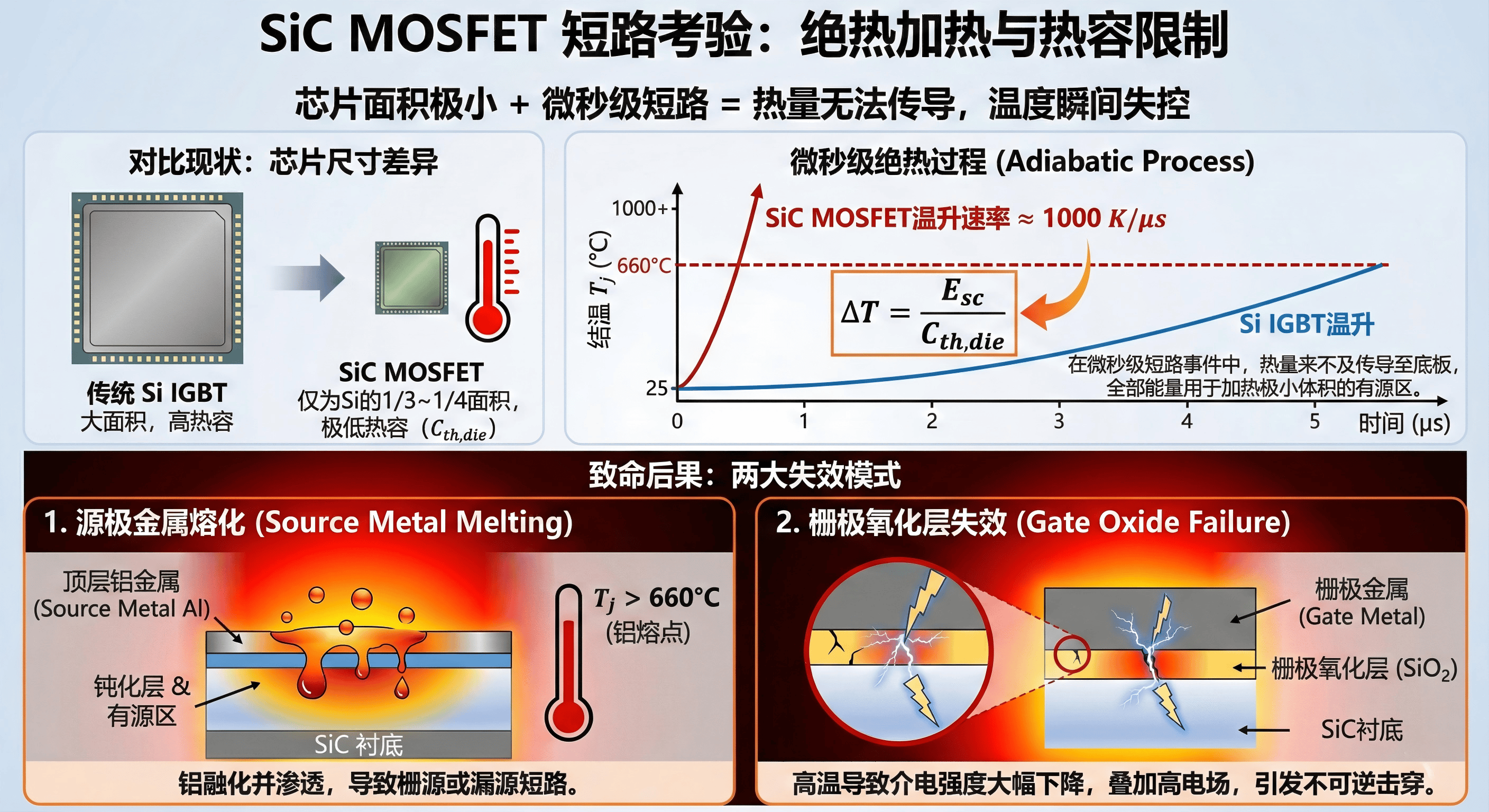

2.2 绝热加热与热容限制

SiC芯片的另一大特征是其极小的芯片面积。对于相同的电压和电流等级,SiC MOSFET的芯片面积通常仅为Si IGBT的1/3到1/4 。虽然SiC材料本身的热导率(4.9 W/(cm⋅K))优于硅(1.5 W/(cm⋅K)),但在微秒级的短路事件中,热量根本来不及传导到底板或散热器。这是一个典型的绝热过程(Adiabatic Process) 。

在绝热条件下,温升仅取决于能量注入与芯片有源区的热容(Thermal Capacity)。

ΔT=Cth,dieEsc

由于芯片体积小,Cth,die极小。这导致结温(Tj)以极高的速率(可达 1000 K/μs)飙升。

失效模式:

- 源极金属熔化: 当结温超过660∘C(铝的熔点)时,顶层铝金属融化并渗透进钝化层,导致栅源短路或漏源短路 。

- 栅极氧化层失效: 高温下,栅极氧化层(SiO2)的介电强度大幅下降,叠加高电场应力,导致栅极不可逆击穿 。

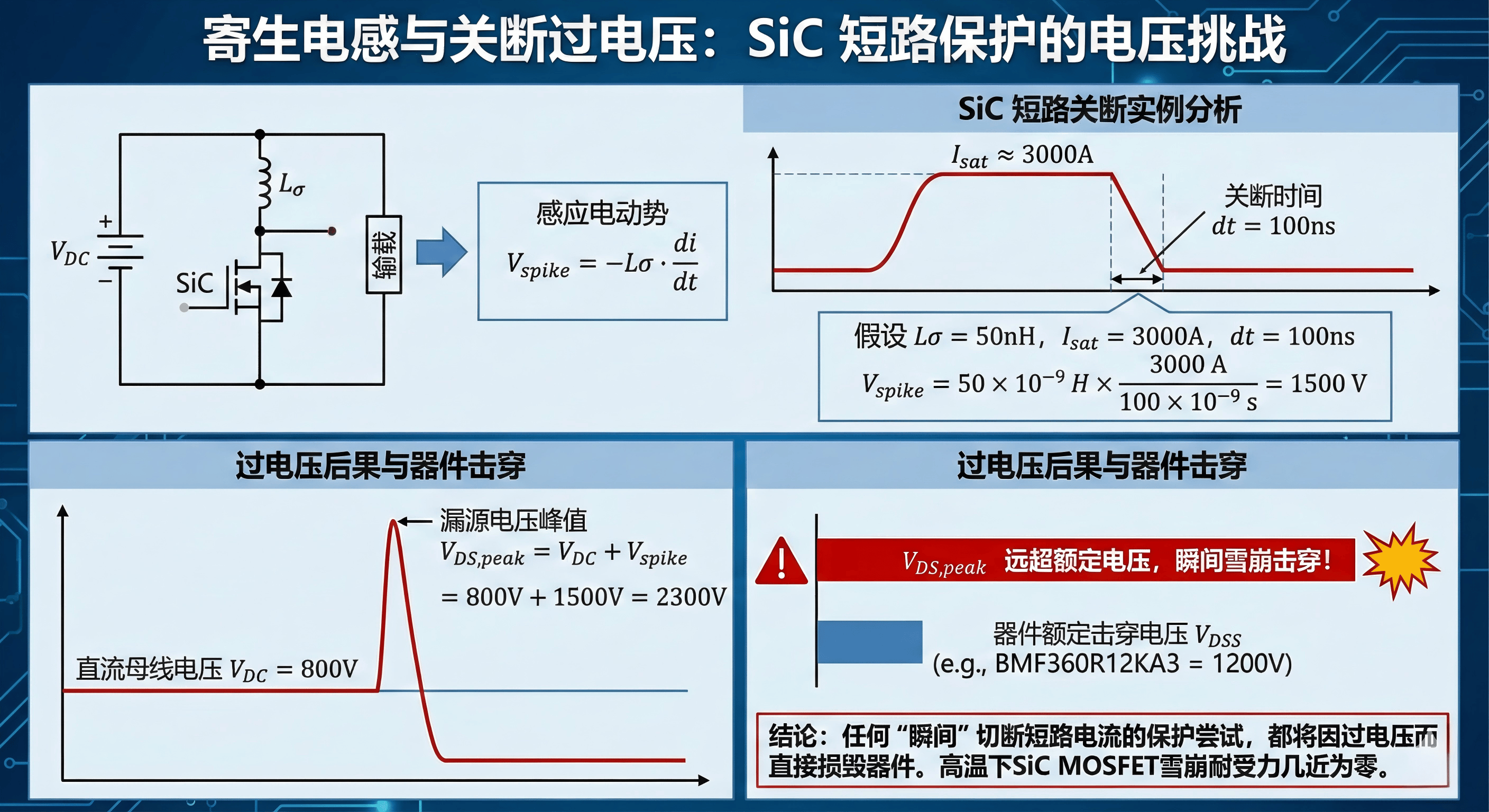

2.3 寄生电感与关断过电压

短路电流不仅带来热问题,更在关断时刻带来电压问题。电力电子回路中不可避免地存在杂散电感(Lσ),包括PCB走线、电容ESL、模块内部键合线等。根据法拉第电磁感应定律,在切断电流时会产生感应电动势:

Vspike=−Lσ⋅dtdi

在SiC系统中,由于Isat极大(例如3000A),即使以常规速度关断,其di/dt也极其惊人。假设回路电感仅为50nH(这在模块应用中已属优秀设计),若在100ns内关断3000A电流:

Vspike=50×10−9 H×100×10−9 s3000 A=1500 V

若直流母线电压为800V,叠加后的漏源电压峰值(VDS,peak)将达到2300V,远超1200V器件的额定击穿电压(如BMF360R12KA3的VDSS=1200V )。这将导致器件立刻发生雪崩击穿。虽然SiC MOSFET具备一定的雪崩耐受能力(Avalanche Ruggedness) ,但在短路高温状态下,器件对雪崩能量的承受力几乎为零 。

因此,任何试图“瞬间”切断短路电流的保护尝试,都将因过电压而直接损毁器件。

3. 传统保护方案的局限性分析

为了应对上述挑战,业界尝试了多种保护方案,但对于SiC MOSFET而言,它们均存在致命缺陷。

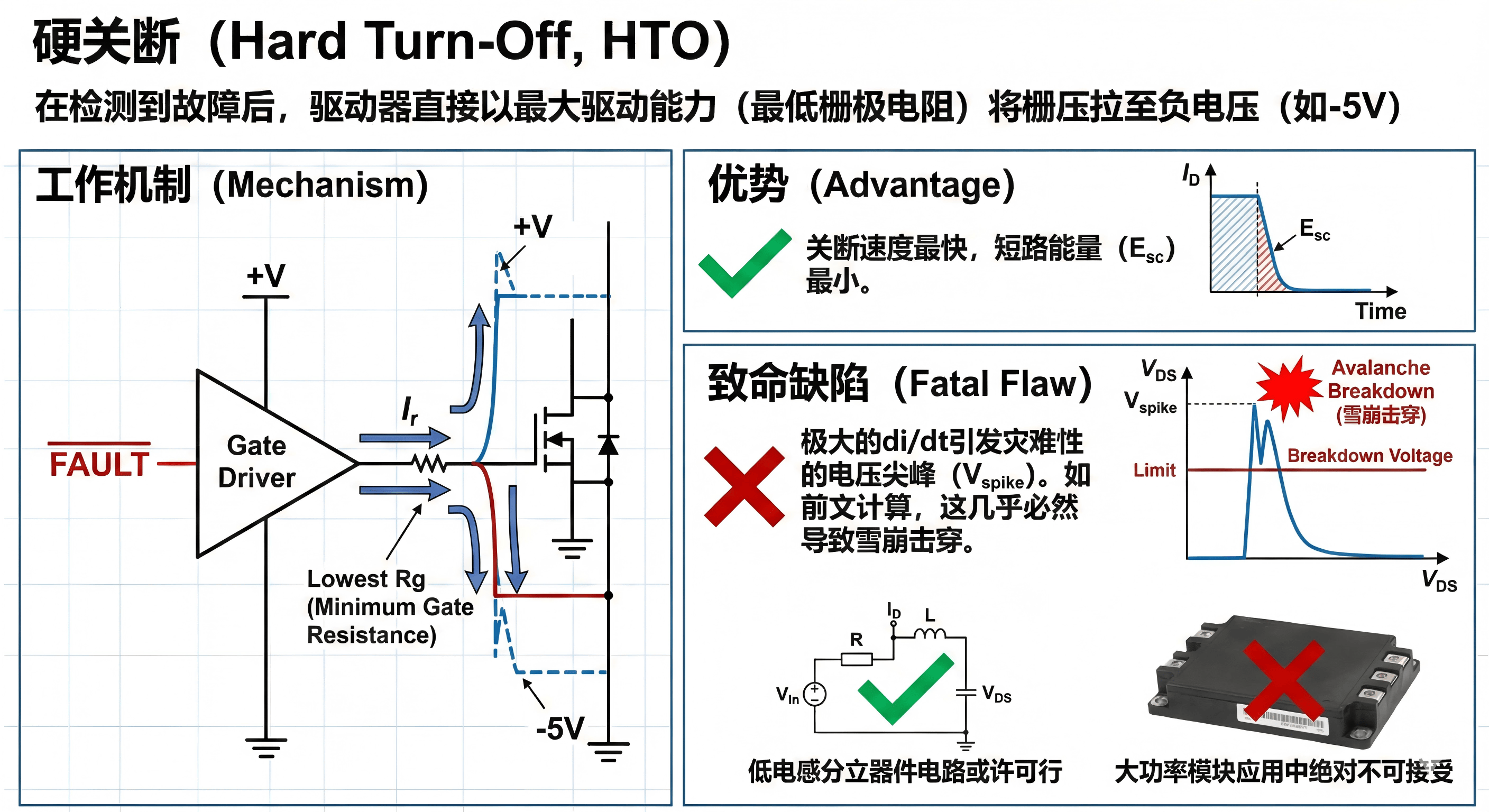

3.1 硬关断(Hard Turn-Off, HTO)

硬关断是指在检测到故障后,驱动器直接以最大驱动能力(最低栅极电阻)将栅压拉至负电压(如-5V)。

- 优势: 关断速度最快,短路能量(Esc)最小。

- 致命缺陷: 极大的di/dt引发灾难性的电压尖峰(Vspike)。如前文计算,这几乎必然导致雪崩击穿。对于低电感分立器件电路或许可行,但在大功率模块应用中绝对不可接受 。

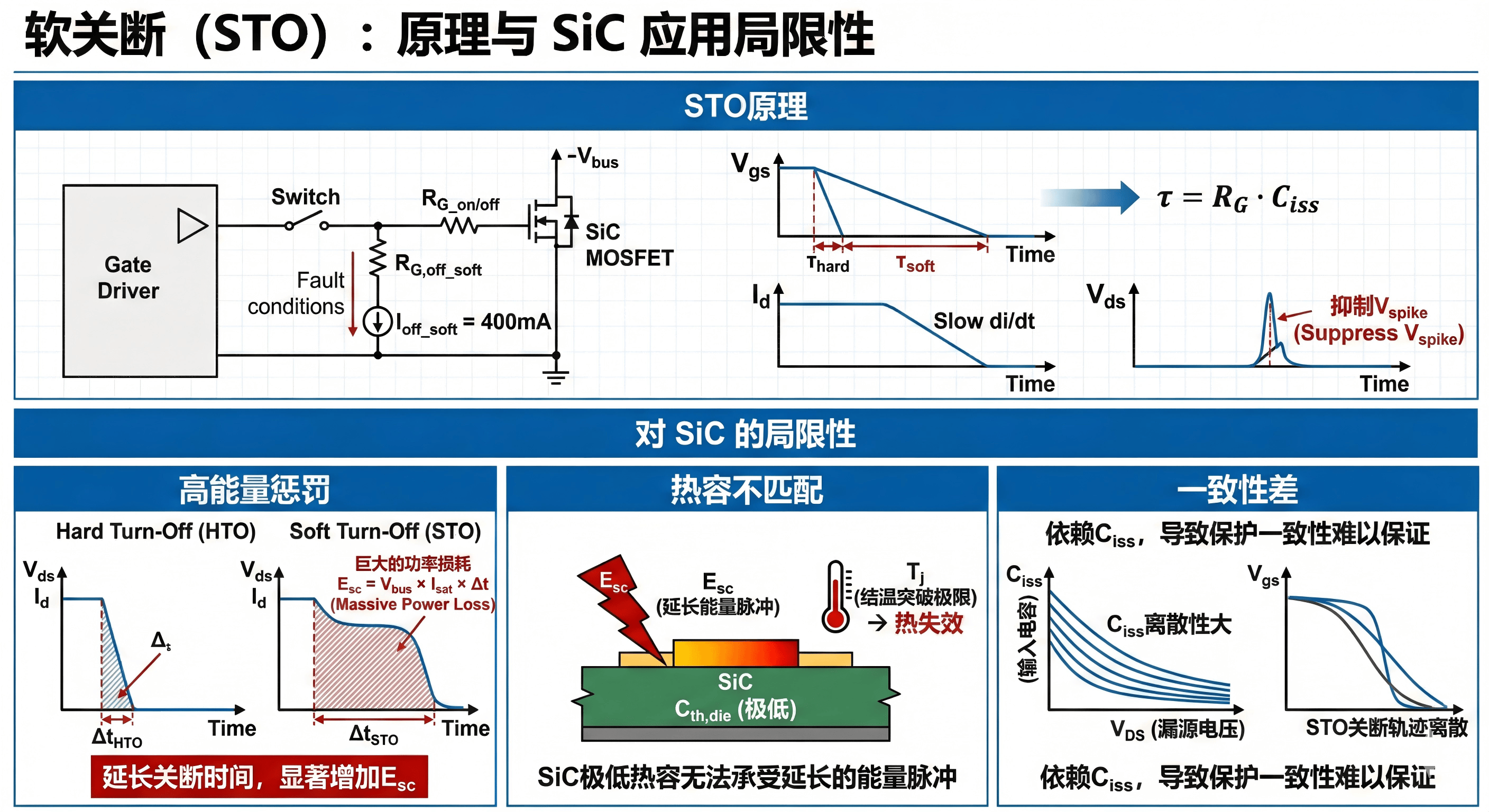

3.2 软关断(Soft Turn-Off, STO)

软关断是目前IGBT驱动中应用最广泛的技术。其原理是在检测到故障后,切换到一个高阻值的关断电阻(RG,off_soft),或者使用一个微小的恒定电流源(如400mA )来缓慢释放栅极电荷。

原理: 通过增大栅极放电的时间常数(τ=RG⋅Ciss),降低栅极电压下降速率,从而限制电流下降率di/dt,进而抑制电压尖峰。

对SiC的局限性(能量惩罚):

- 时间换电压的代价过高: 为了将电压尖峰压制到安全范围,STO必须显著延长关断时间。在这一延长的过程中,器件仍处于高导通状态,电流维持在饱和水平,电压维持在母线电压。这意味着器件在“慢关断”期间承受着巨大的功率损耗。

- 热容不匹配: SiC极低的热容无法承受这种延长的能量脉冲。研究表明,采用STO策略时,为了安全抑制电压,往往会导致短路能量Esc增加一倍以上,直接导致结温突破极限引发热失效 。

- 一致性差: STO的关断轨迹高度依赖于器件的输入电容Ciss。而SiC MOSFET的Ciss随VDS变化剧烈,且不同厂家、不同批次的离散性较大,导致保护的一致性难以保证 。

表格 1:传统保护策略对比

保护策略关断速度电压尖峰 (Vspike)短路能量 (Esc)适用性分析硬关断 (HTO)极快 (< 200ns)极高 (易击穿)最低仅适用于极低电感的小功率电路,大功率模块禁用。软关断 (STO)慢 (> 2-5µs)低 (安全)极高 (易过热)适合热容大的IGBT,不适合热容小且饱和电流大的SiC MOSFET。

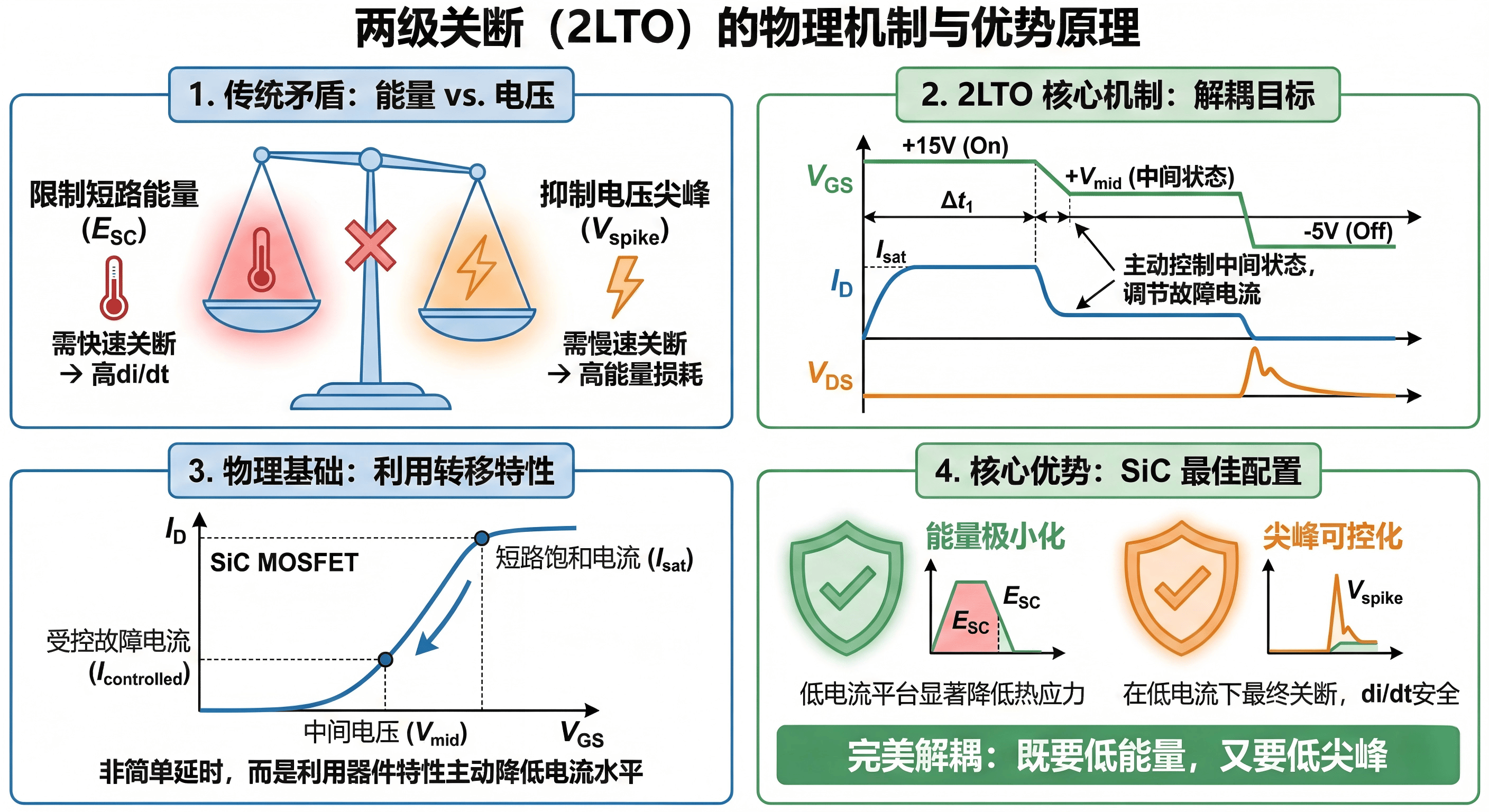

4. 两级关断(2LTO)的物理机制与优势原理

两级关断(Two-Level Turn-Off, 2LTO)技术之所以成为SiC MOSFET短路保护的最佳配置,根本原因在于它解耦了“限制短路能量”与“抑制电压尖峰”这两个看似矛盾的目标。它通过主动控制栅极电压的中间状态,利用SiC器件本身的转移特性来调节故障电流,而非简单地延长时间。

4.1 2LTO的工作时序与机制

2LTO的操作过程可以精确划分为两个核心阶段:

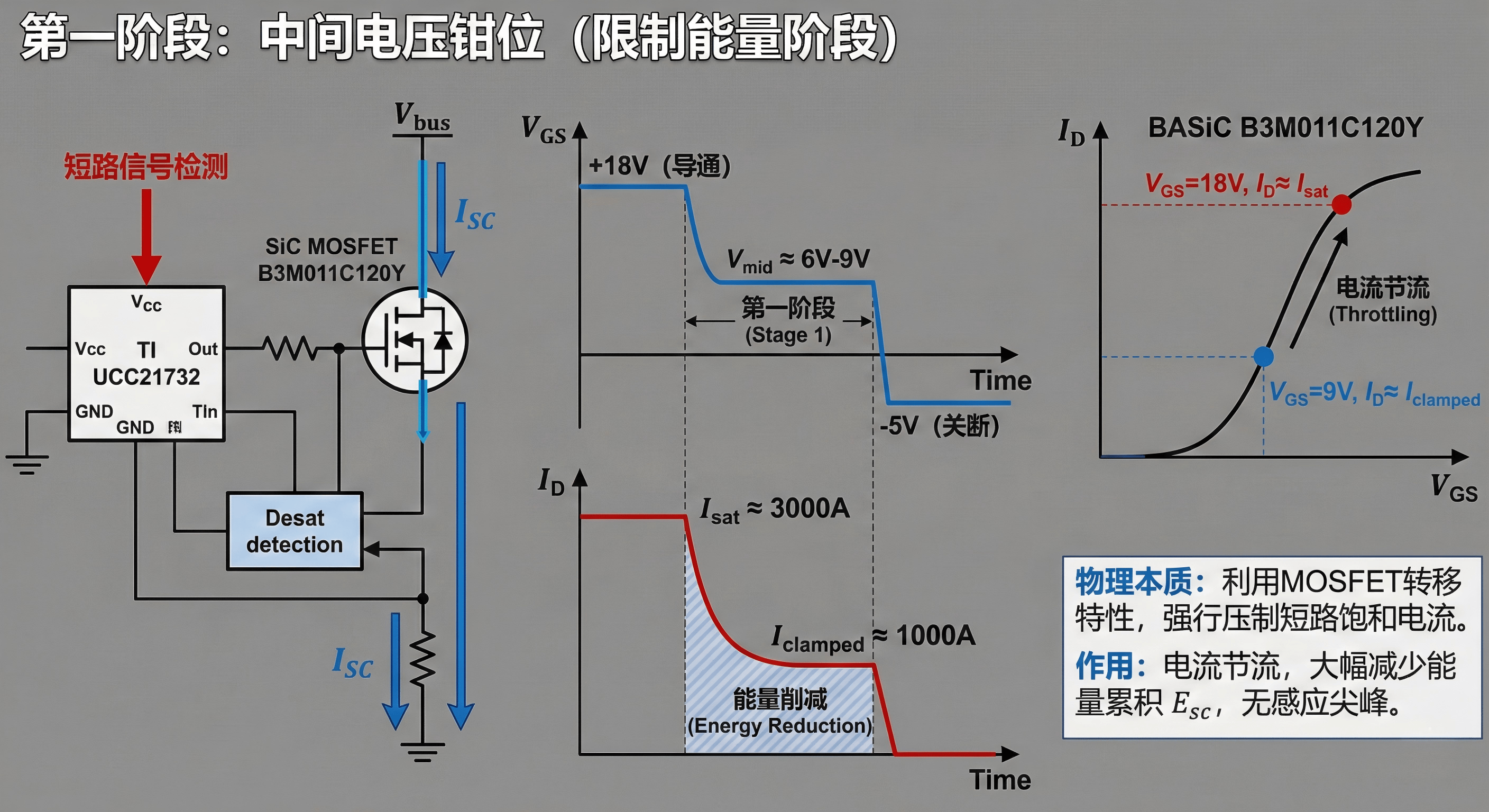

第一阶段:中间电压钳位(限制能量阶段)

当驱动芯片(TI的UCC21732)通过Desat或分流器检测到短路信号后,不立即完全关断,而是迅速将栅源电压(VGS)从导通电平(+18V)拉低到一个预设的中间电压平台(Intermediate Voltage Plateau, Vmid) ,通常设定在6V至9V之间。

物理本质: 利用MOSFET的转移特性(Transfer Characteristic)。SiC MOSFET的漏极电流ID与VGS呈强非线性关系。

- 查看BASiC B3M011C120Y的数据手册,在25∘C下,VGS=18V时ID≈180A(饱和区甚至更高),而当VGS降至9V时,ID迅速下降至约40A左右(具体数值依转移曲线而定)。

作用:

- 电流节流(Throttling): 在器件仍然导通的情况下,强行将巨大的短路饱和电流(如3000A)压制到一个较低的水平(如1000A)。

- 能量削减: 由于电流被大幅压制,第一阶段剩余时间内的瞬时功率(P=Vbus×Iclamped)显著降低,从而大幅减少了累积热量Esc。

- 无感应尖峰: 此阶段虽然电流下降,但由于MOSFET仍处于导通区(或进入线性区边缘),沟道阻抗增加吸收了能量,且电流并未切断,因此不会产生关断过电压。

第二阶段:延迟完全关断(安全换流阶段)

在中间电压平台维持一段固定的延迟时间(thold,通常为500ns至2µs)后,驱动器将栅压拉低至关断负压(-5V)。

- 物理本质: 切断剩余的电流。

- 作用: 此时需要切断的电流已经从3000A降至了1000A(假设值)。

- 结果: 根据Vspike=L⋅di/dt,由于起始电流大幅降低(ΔI减小),最终关断产生的电压尖峰成比例地缩小。这使得系统可以在不增加外部栅极电阻RG的情况下,安全地关断短路故障。

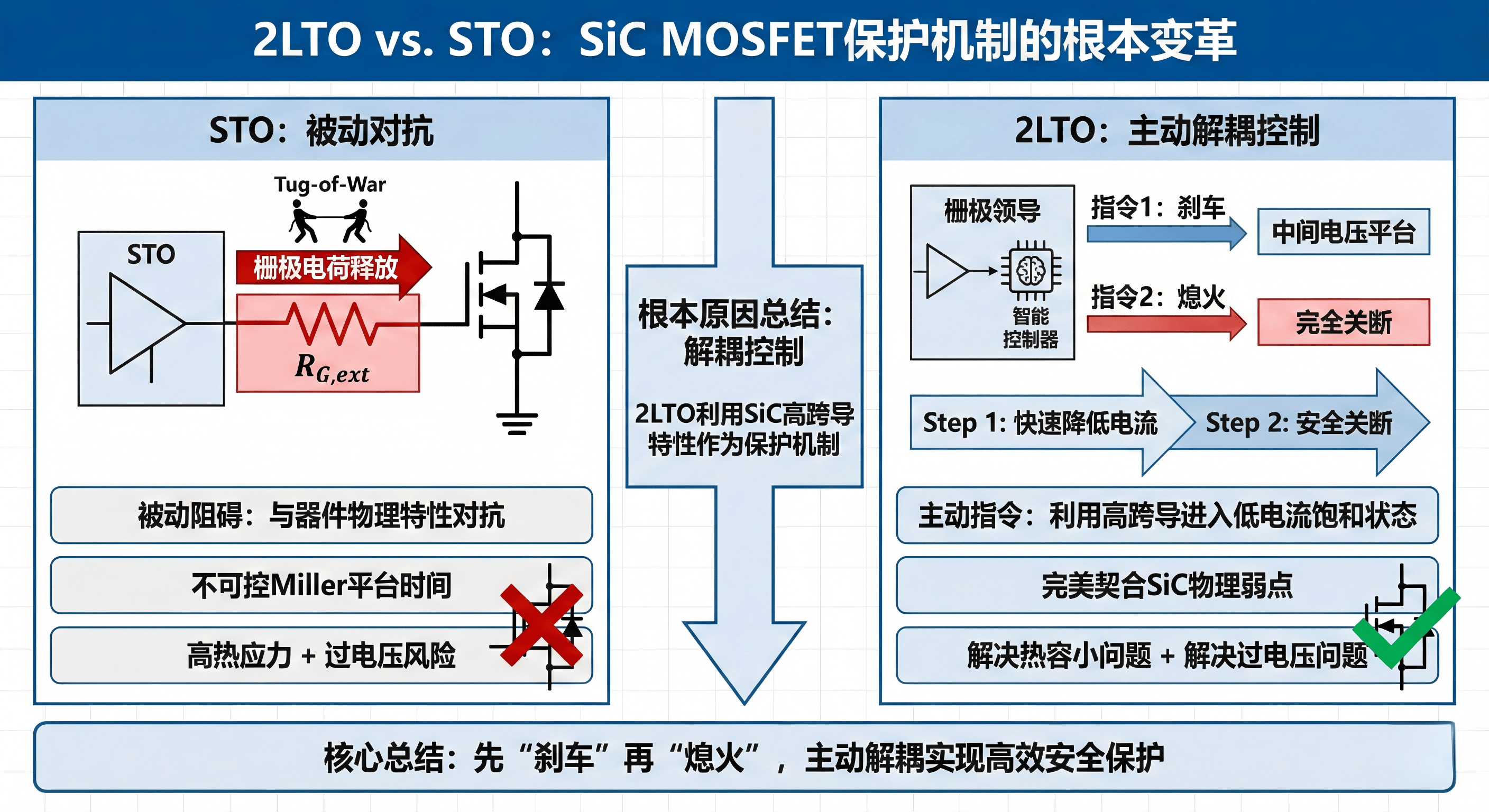

4.2 根本原因总结:解耦控制

2LTO的根本优势在于它利用了SiC MOSFET的高跨导特性作为保护机制的一部分。

- STO 试图通过外部电阻“被动”地阻碍栅极电荷释放,这是一种与器件物理特性对抗的过程(增加了不可控的Miller平台时间)。

- 2LTO 则是“主动”地指令器件进入一个低电流饱和状态。它先“刹车”(降低电流),再“熄火”(完全关断)。

这种机制完美契合SiC MOSFET的物理弱点:

- 它通过快速进入中间平台,解决了热容小、不能承受长时间高功率的问题。

- 它通过降低最终关断电流,解决了开关速度快、寄生电感敏感导致的过电压问题。

4.3 与竞争方案的量化对比

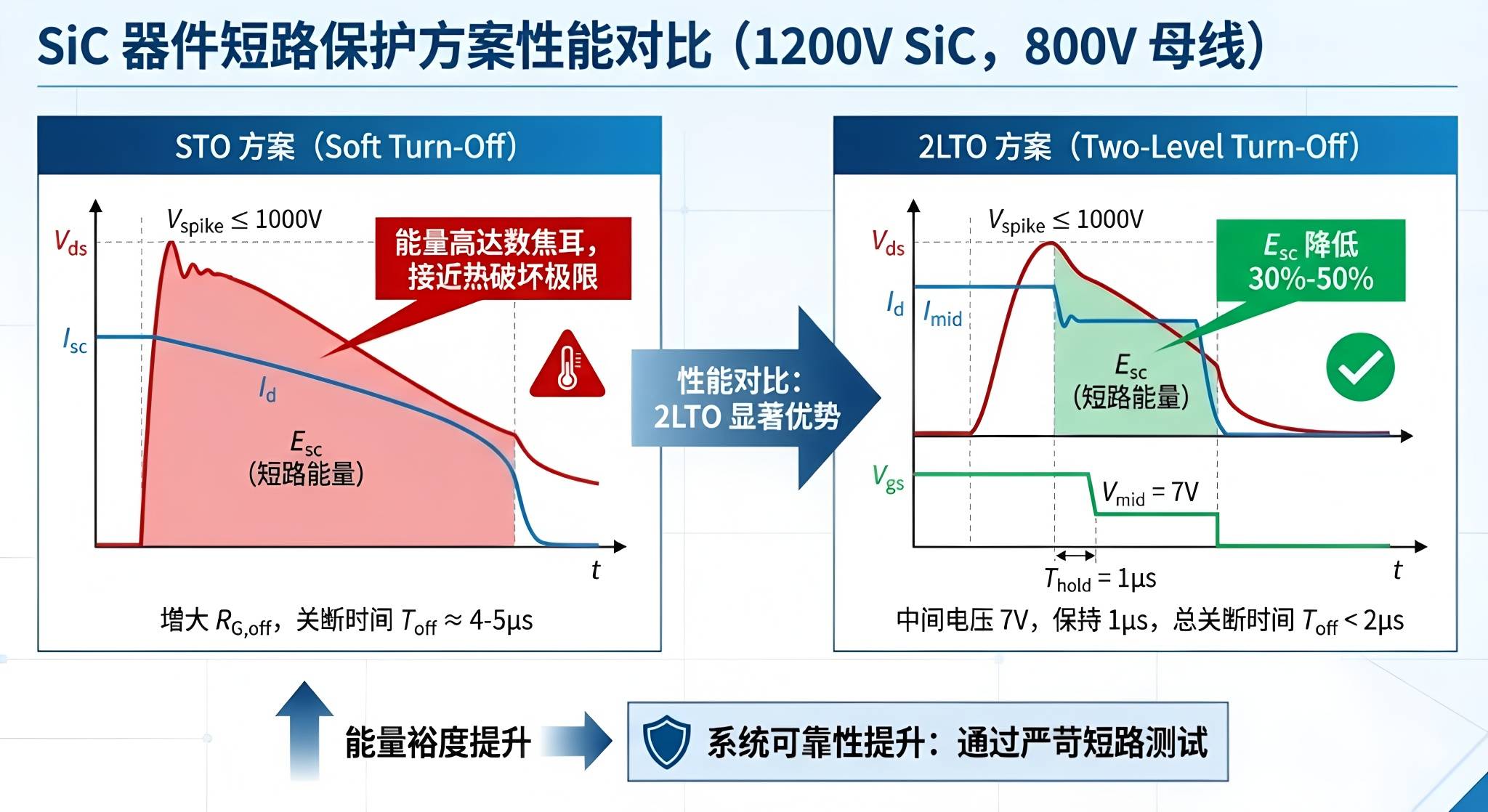

根据研究数据 ,在同等测试条件下(1200V SiC器件,800V母线):

- STO方案: 若要将电压尖峰控制在1000V以内,需显著增大RG,off,导致关断时间延长至4-5μs,短路能量Esc可能高达数焦耳,接近器件热破坏极限。

- 2LTO方案: 设定中间电压7V,保持1μs。总关断时间可控制在2μs以内,且电压尖峰同样控制在1000V以内,但Esc可降低30%-50%。

这种能量裕度的提升,直接转化为系统可靠性的提升,使得SiC模块能够通过严苛的短路测试。

5. 关键设计参数的优化与工程实践

2LTO并非“即插即用”,其效能高度依赖于中间电压电平(Vmid)和保持时间(thold)的精确配置。

5.1 中间电压平台(Vmid)的选择

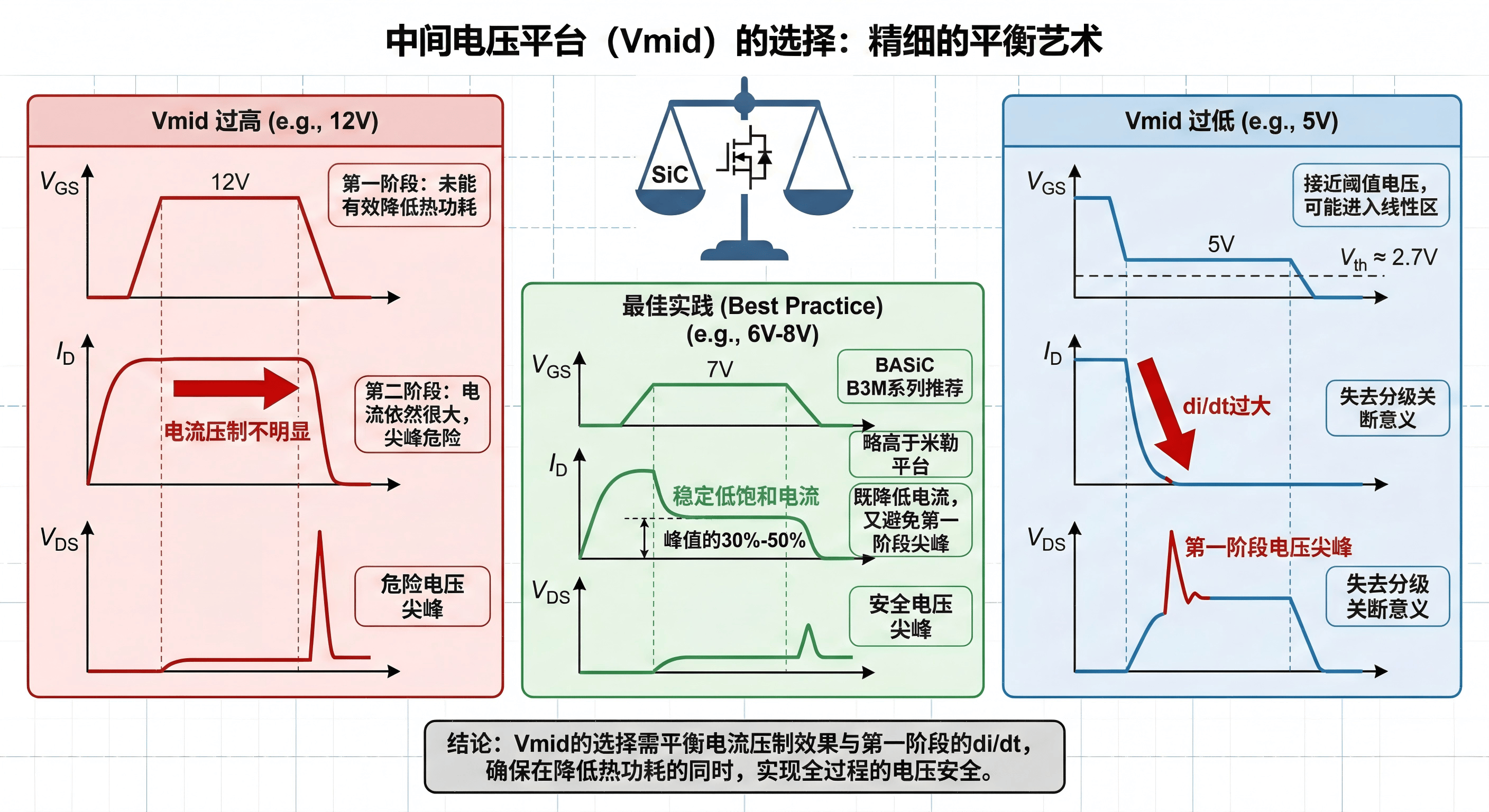

Vmid的选择是一个精细的平衡艺术:

- Vmid 过高(如12V): 电流压制效果不明显,第一阶段未能有效降低热功耗,第二阶段关断时电流依然很大,电压尖峰依然危险。

- Vmid 过低(如5V): 接近阈值电压(Vth≈2.7V )。此时器件可能会进入线性区,或者电流下降过快。如果在第一阶段电流下降太快(di/dt过大),那么第一阶段本身就会产生巨大的电压尖峰,失去了分级关断的意义 。

最佳实践: 根据BASiC B3M系列的数据,推荐的Vmid通常设定在6V ~ 8V之间。这一电压值通常略高于米勒平台电压,能够确保器件处在一个稳定的低饱和电流状态,既能显著降低电流(通常降至峰值的30%-50%),又不会引发第一阶段的过电压振荡 。

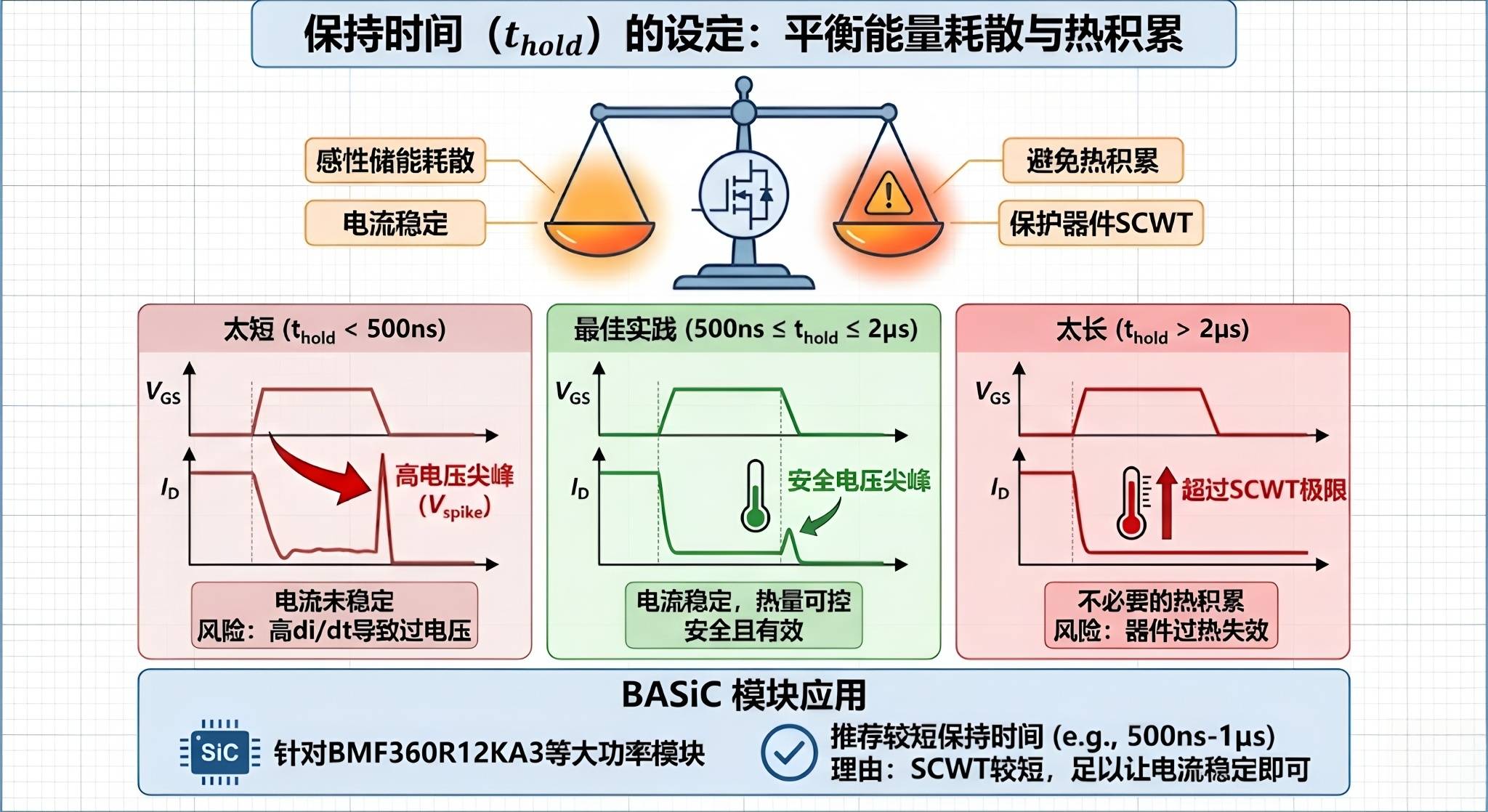

5.2 保持时间(thold)的设定

保持时间必须足够长,以允许电路中的感性储能通过器件通道进行耗散,并让电流稳定在低水平;但又不能太长,以免造成不必要的热积累。

- 一般建议: thold 设定在 500ns 至 2µs 之间。

- BASiC模块应用: 考虑到BMF360R12KA3等大功率模块的SCWT较短,较短的保持时间(如500ns-1µs)更为安全,只要足以让电流稳定即可。

5.3 栅极驱动电路的实现

现代SiC专用栅极驱动芯片已内置2LTO功能。:

- Infineon 1ED3321MC12N: 通过“Soft-off”功能实现,虽然名为Soft-off,但其内部机制可通过配置实现类似的分级效果 16。

- TI UCC21732: 提供了专门的“2LTOFF”引脚或逻辑,允许用户通过外部电阻网络精确设定Vmid和thold,完全解耦正常开关与故障保护的逻辑 。

对于分立驱动方案,设计者通常利用两个串联的关断路径:一个通过低阻路径连接到Vmid源,另一个通过延迟电路连接到VEE。

6. 案例研究:BASiC Semiconductor SiC模块的应用

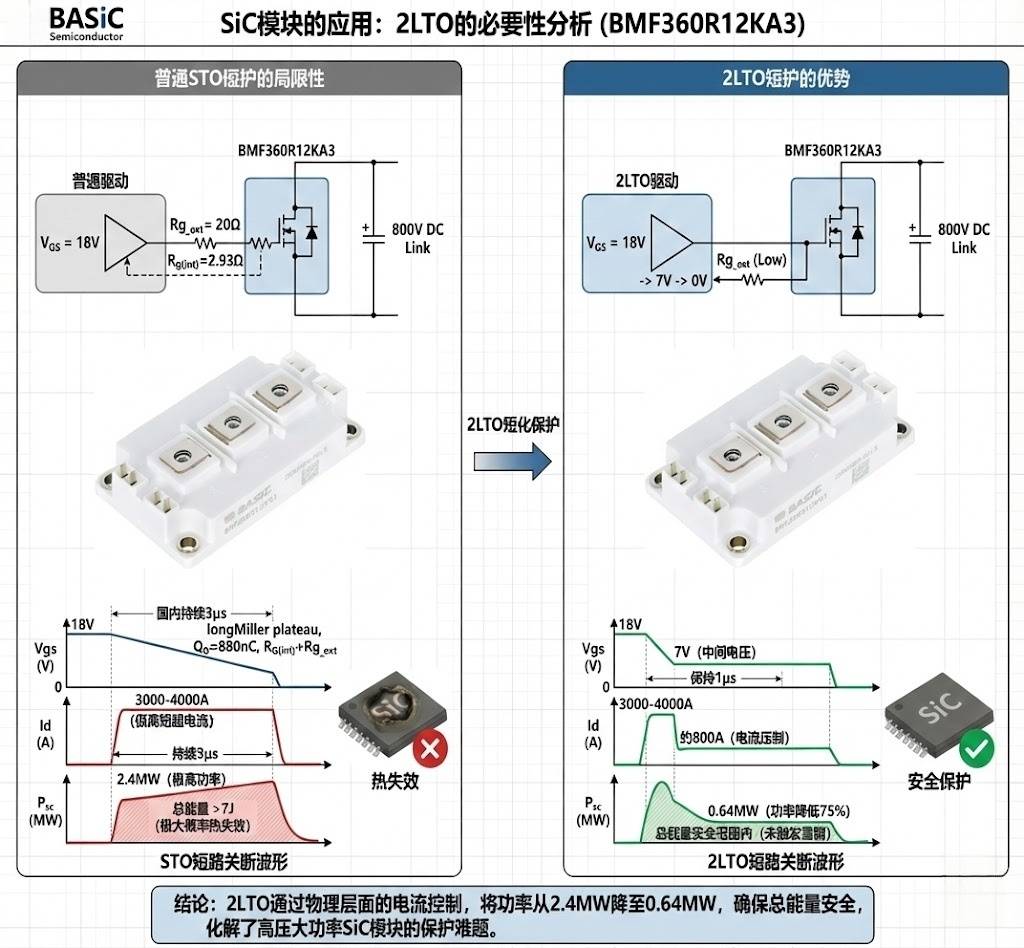

以BASiC Semiconductor的BMF360R12KA3(1200V/360A)模块为例,分析2LTO的必要性。

6.1 器件特性分析

- 额定电流: 360A。

- 脉冲电流极限: 720A 。

- 短路电流估算: 基于SiC的高跨导特性,该模块在18V栅压下的短路饱和电流可能高达3000A-4000A。

- 内部栅极电阻: RG(int)=2.93Ω 6。这相对较高的内阻意味着即使外部短路栅极电阻为0,关断速度也受限于内部RC常数。

6.2 保护策略仿真

若采用普通STO(如通过20Ω电阻关断):

- 由于QG=880 nC 6较大,且内部存在2.93Ω电阻,外部再串联大电阻会导致米勒平台时间极度拉长。

- 在整个米勒平台期间,器件承受800V×3000A=2.4MW的功率。

- 若STO持续3μs,总能量超过7J,极大概率导致热失效(通常SiC模块的临界能量在1-2J左右 )。

若采用2LTO(中间电压7V):

- 故障检测后(如500ns),栅压瞬降至7V。

- 根据转移特性,电流被迅速压制至约800A。

- 在接下来的1μs保持时间内,功率降为800V×800A=0.64MW。

- 相比STO,功率降低了近75%。

- 最后关断时,仅需切断800A电流,电压尖峰极小。

- 总能量控制在安全范围内,且未触发雪崩。

这一案例清晰展示了2LTO如何通过物理层面的电流控制,化解了高压大功率SiC模块的保护难题。

7. 结论

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

驱动IC的**两级关断(2LTO)**技术成为碳化硅MOSFET短路保护的最佳配置,并非一种偶然的工程选择,而是由碳化硅材料及其器件结构的物理特性所决定的必然结果。

其根本原因在于:SiC MOSFET极短的短路耐受时间(热限制)与极高的开关速度及电流密度(电压限制)之间存在不可调和的矛盾。 传统的硬关断触犯了电压限制,软关断触犯了热限制。而2LTO通过引入中间电压状态,利用器件的高跨导特性,将短路保护过程分解为“电流限幅”和“最终关断”两个解耦的步骤。

- 主动限流: 通过降低栅压,主动限制短路电流,从源头上削减了导致热失效的能量输入。

- 降低感应电势: 通过降低最终关断时的电流幅值,从物理上减小了di/dt,从而在不牺牲关断速度的前提下消除了过电压风险。

- 鲁棒性: 提供了比被动电阻放电(STO)更确定、更可控、受参数离散性影响更小的保护轨迹。

对于追求高可靠性的SiC电源系统设计者而言,理解并应用2LTO技术,是释放SiC潜能、确保系统在极端故障下依然安全存活的关键所在。随着如主流厂商推出的新一代集成2LTO功能的驱动芯片和高性能模块,这一保护策略已成为行业事实上的标准配置。