晶振阻抗详解:频率稳定的三个步骤

创始人

2025-08-23 10:07:48

0次

在微控制器、系统级芯片以及通信芯片中,晶振是保证系统稳定运行的核心时钟源。在设计和调试过程中,难免会遇到如下问题:电路不起振、起振时间过长、输出波形畸变、频率偏差过大等。这些现象大多与晶振阻抗密切相关。

今天KOAN凯擎小妹带大家了解一下晶振阻抗的三个步骤:

查看阻抗曲线 → 调负载电容 → 计算负性阻抗

第一步:看阻抗曲线

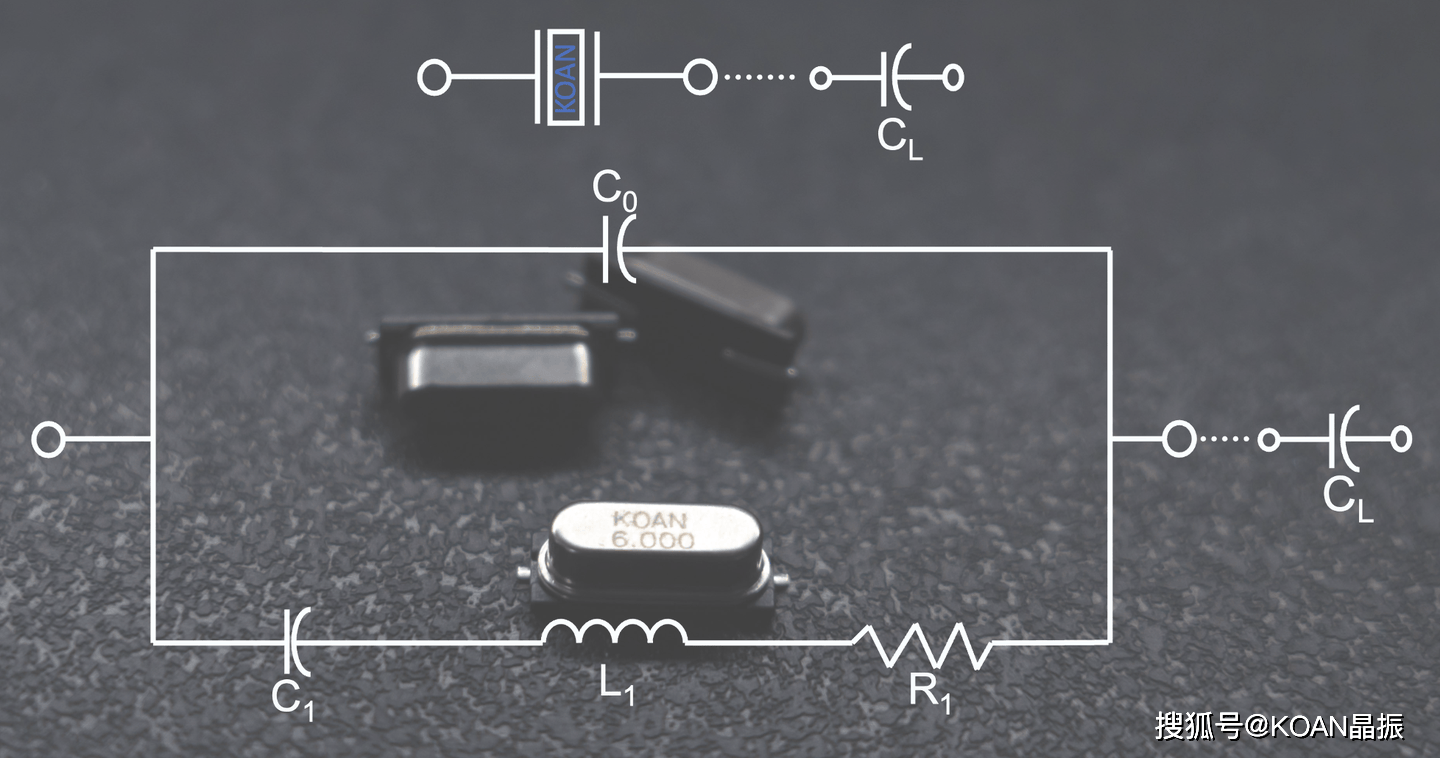

晶振的等效电路通常包含四个参数:

- L1:等效电感(机械惯性)

- C1:等效电容(弹性恢复力)

- R1:等效电阻(能量损耗)

- C0:寄生电容(电极间静电效应)

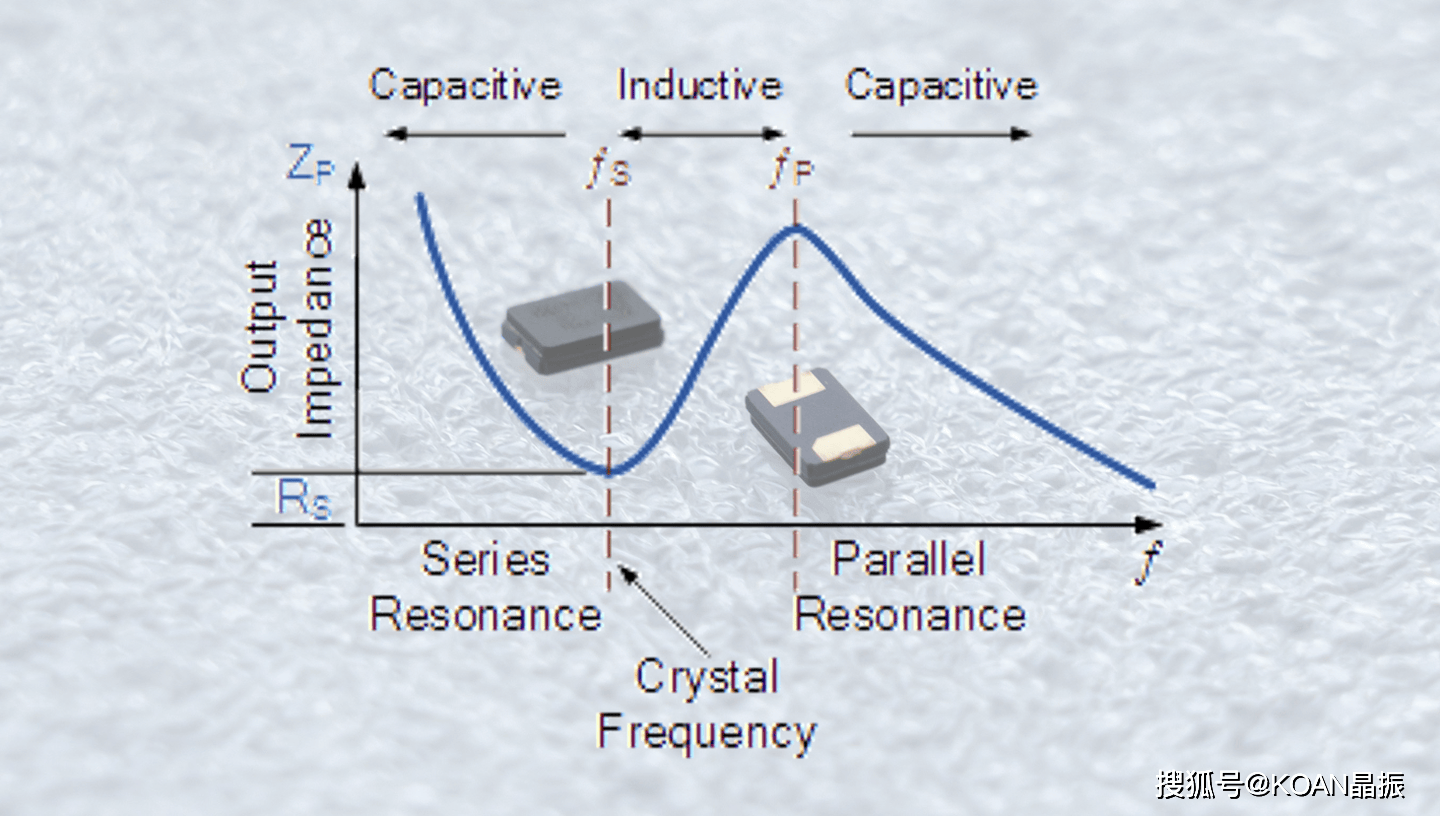

通过观察晶振的阻抗曲线,可以了解晶振在不同频点下的表现:

- 串联谐振点fs:等效电感L1与等效电容C1相互抵消,阻抗降至最低,仅剩等效电阻R1。在图中对应Rs点(即 ESR)。此时晶体最容易振荡。

- 并联谐振点fp:晶体与寄生电容C0共同作用,使阻抗升至最高,在图中对应Zp点,接近开路。这个点决定了电路最终的工作频率。

- 其他频率区间:阻抗随频率变化而不稳定,要么偏高,要么偏低,晶体表现为电容性或电感性。电路的实际工作点通常落在fs与fp之间的区间。

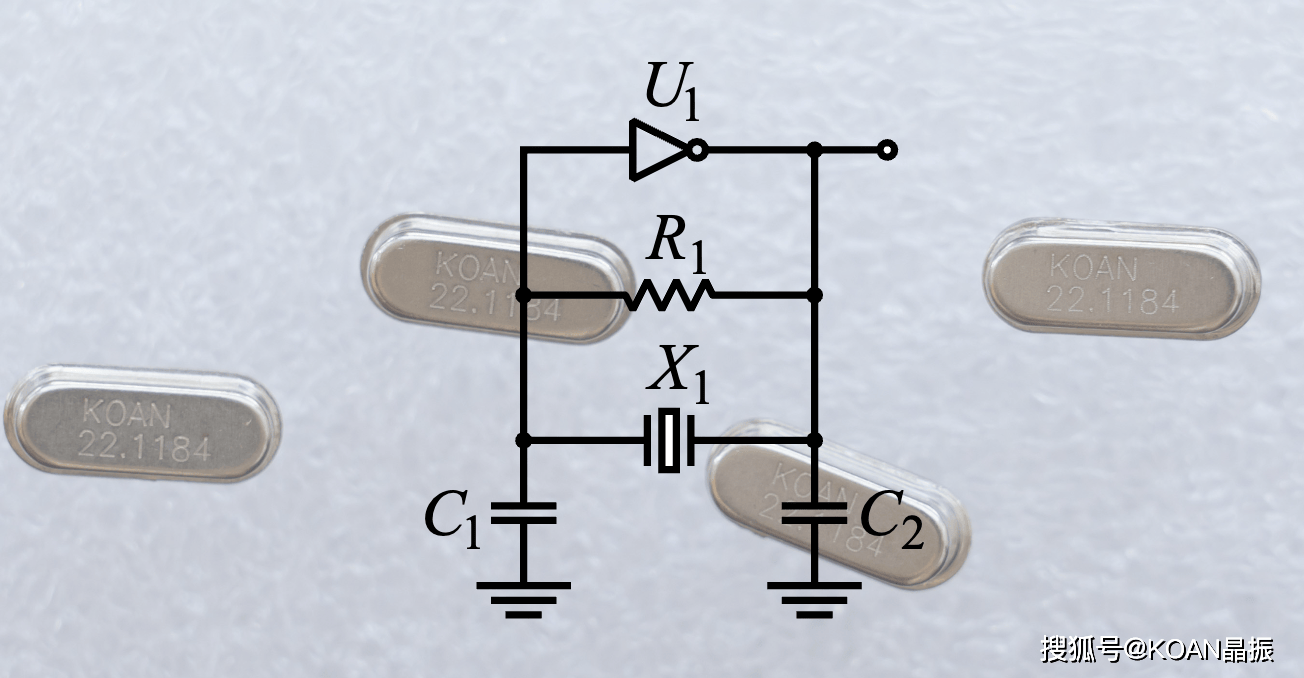

第二步:调负载电容

在确定阻抗曲线之后,需要利用外部电容C1和C2对电路的工作点进行微调。它们与晶体的寄生电容C0共同形成等效负载电容CL,决定晶振在fs与fp之间的确切位置,从而使实际工作频率校准到标称值。

在并联振荡器(如皮尔斯振荡器)中,这两个外部电容是必不可少的,直接影响电路能否在目标频率上稳定振荡。

- 电容过大 → 振荡频率降低

- 电容过小 → 振荡频率升高

- 偏差过大 → 可能导致不起振或波形畸变

第三步:计算负性阻抗

即使电容匹配正确,如果驱动不足,振荡仍可能无法启动。这涉及负性阻抗(-R)。振荡电路中,放大器必须提供足够的负性阻抗抵消晶体等效电阻ESR。

建议振荡宽限为晶振等效串联电阻RR的5倍之上:

|-R| ≥ 5RR

- |-R| 太小 → 起振慢或不起振

- |-R| 太大 → 晶体过热、老化加速

KOAN凯擎小妹建议

- ESR参数匹配:不同晶体的等效串联阻抗ESR差异大,要与芯片手册匹配。

- 驱动能力适中:部分MCU振荡器可调驱动电流,避免过驱。

- PCB布局优化:晶体与芯片走线尽量短、靠近接地,减少寄生电容。

- 测试谨慎:示波器探头会增加电容,导致频率偏差。

相关内容

热门资讯

华天科技:绿色智造引领半导体可...

在全球绿色变革的浪潮中,工业制造正面临一场深刻的生态转型。作为中国半导体封装测试行业的领军企业,华天...

深南电路(002916)12月...

证券之星消息,截至2025年12月22日收盘,深南电路(002916)报收于226.0元,上涨6.2...

信音电子(301329)12月...

证券之星消息,截至2025年12月22日收盘,信音电子(301329)报收于23.87元,下跌1.6...

奕东电子(301123)12月...

证券之星消息,截至2025年12月22日收盘,奕东电子(301123)报收于60.44元,上涨6.6...

禾润电子等4家公司启动IPO辅...

每经AI快讯,证监会网站显示,近日,禾润电子科技(嘉兴)股份有限公司、鑫精合激光科技集团股份有限公司...

英伟达 、SK海力士与群联电子...

12月23日消息,据报道,英伟达与韩国SK海力士共同开发新型人工智能(AI)固态硬盘,群联电子也参与...

英伟达 、SK海力士与群联电子...

英伟达据悉携手韩国SK海力士打造新型人工智能(AI)固态硬盘,群联电子也参与开发。新型人工智能专用固...

股市必读:亚世光电(00295...

截至2025年12月22日收盘,亚世光电(002952)报收于19.94元,下跌1.29%,换手率2...

西园街道嵌入式服务设施建设

采购人名称 合肥市蜀山区西园街道办事处 中标(成交)供应商名称 安徽峰...

应对存储芯片涨价 一家PC高管...

受全球内存供应“超级周期”的影响,PC行业正面临一场波及全产业链的涨价风暴。包括联想、戴尔、惠普、宏...