如何避免MOS管在开关过程中的电压尖峰?

MOS管(金属氧化物半导体场效应晶体管)在开关过程中易产生电压尖峰,可能引发器件损坏或电磁干扰问题。为有效抑制电压尖峰,需从电路设计、器件选型、布局布线及保护措施等多维度进行优化,以下为具体解决方案:

1. 优化驱动电路设计

驱动电阻调整:在MOS管栅极串联合适电阻(如10Ω~100Ω),可减缓栅极电压变化速率,抑制开关瞬态电流。需平衡开关速度与尖峰幅度,避免电阻过大导致开关损耗增加。

栅极驱动芯片选型:选用具备米勒钳位(Miller Clamp)或负压关断功能的驱动芯片。米勒钳位在关断时将栅极电压拉低至负压,防止米勒电容效应引发误开通;负压关断(如-5V)可加速关断过程,减少电压过冲。

驱动电路布局:缩短栅极驱动回路路径,降低寄生电感。采用同层铺铜、减小走线长度等措施,减少驱动信号与功率回路的耦合。

2. 降低电路寄生参数

PCB布局优化:功率回路(如漏极-源极)走线应宽且短,避免环路面积过大。例如,将输入电容、MOS管、负载三者紧密排列,减少电流路径的寄生电感。

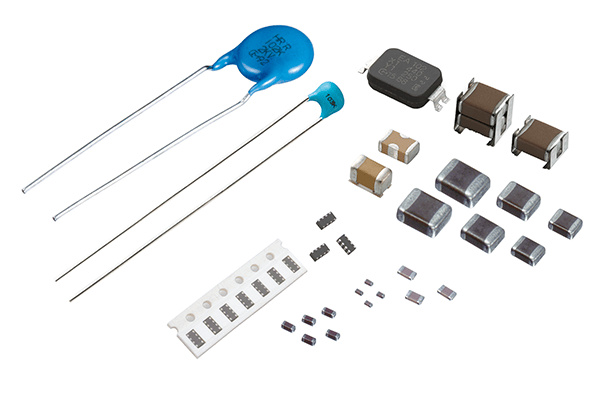

吸收电路设计:在漏极-源极间并联RC缓冲电路(如10Ω电阻+100pF电容)或RCD钳位电路。RC缓冲电路吸收开关瞬态能量,RCD钳位电路将电压尖峰限制在安全范围内。

去耦电容配置:在电源输入端并联高频去耦电容(如0.1μF陶瓷电容),降低电源阻抗,抑制电压波动。

3. 器件选型与参数匹配

选择低寄生参数器件:选用封装寄生电感小的MOS管(如DFN封装),并匹配低ESL的输入电容。

电压与电流裕量设计:MOS管耐压值应高于工作电压的1.5~2倍,电流额定值需满足峰值电流需求,避免过载导致电压尖峰。

4. 软开关技术

谐振电路引入:在开关电路中加入谐振电感与电容,实现零电压开关(ZVS)或零电流开关(ZCS)。例如,LLC谐振变换器通过谐振使MOS管在电压或电流过零时切换,消除开关损耗与尖峰。

通过上述措施,可显著降低MOS管开关过程中的电压尖峰,提升电路可靠性与EMC性能。实际应用中需结合具体电路参数进行仿真与调试,确保优化效果。